當今的設計師面對無數的挑戰:一方面他們必須滿足高技術產品不斷擴展的特性需求,另一方面卻不得不受到無線和電池裝置的電源限制。沒有任何技術在這方面的要求比SoC的設計更為明顯,在這種設計中,高級工藝比從前復雜的多。然而,上述技術造成了新的電源問題。現代SoC系統的關鍵之一就是:嵌入存儲器在芯片中的比例在不斷增長。當存儲器開始主導SoC時,應用節能技術使存儲器獲得系統電源變得十分重要。重要問題之一就是:在系統結構方面,是嵌入系統存儲器還是把存儲器放在SoC之外。在以前的技術中,電源不是要考慮的一個主要因素,而成

關鍵字:

Mosys SoC ASIC

摘 要:本文研究并開發了一款針對手持設備、內嵌ARM7TDMI內核的系統芯片。在設計這款芯片的過程中,MP3算法的軟硬件分割和芯片的低功耗設計是主要挑戰。本文介紹了該系統芯片的結構,并著重介紹了軟硬件分割和低功耗設計技術。關鍵詞:系統芯片;低功耗;ARM;MP3

引言隨著半導體技術的進步和芯片設計方法—IP重用技術的出現,SoC在消費類電子產品中已經越來越普遍。本課題組去年啟動了稱為Garfield的SoC項目。Garfield定義為一款面向中低端PDA的

關鍵字:

ARM MP3 低功耗 系統芯片 SoC ASIC

摘 要:本文介紹了一種SoC單片機控制的多功能數據采集卡,在輸入通道中增加程控濾波、程控增益放大器和多級陷波電路,采集卡的功能選擇和參數改變均由SoC單片機軟件控制。本文給出了關鍵部分的電路圖、元件參數和實測數據。關鍵詞:SoC 單片機;程控放大;程控陷波

引言目前大多數的數據采集卡并不能適應工業控制現場或像野外那樣存在多種噪聲干擾的使用環境,特別是對50Hz工頻干擾及其諧波干擾無法起到抑制作用。在這種情況下,采集到的數據往往有很多錯誤或者采集卡無法正常工作。本數據采

關鍵字:

SoC 單片機 程控放大 程控陷波 SoC ASIC

摘 要:本文首先介紹了一個32位嵌入式稅控機專用系統芯片C3118的功能、結構和特點,然后分析了一個自動化程度很高的SoC設計平臺——C*SoC200,對該平臺的主要結構和功能進行了分析。關鍵詞:IP;SoC;平臺;仿真

引言2003年7月,中國國家質量監督檢驗檢疫總局發布了由稅控機國家標準制定委員會制定的稅控收款機國家標準。并將陸續出臺一系列的管理法規。為了滿足國家標準的要求,各稅控機生產廠家都在積極使用32位MCU開發符合新規范的稅控機。而32位的嵌入式稅控機專用

關鍵字:

IP SoC 仿真 平臺 SoC ASIC

找到價格、性能和功耗的最佳結合點實際上就確保贏得了SoC設計,但說起來容易做起來難。在實際可用的雙芯核架構、可編程加速器和數百萬門FPGA出現以前,一種80:20法則用起來很奏效:如果計算負荷的80%為數據處理,那么選擇RISC架構,在RISC中實施信號處理。而當今面臨太多的架構選擇,差別甚微,用單一處理器架構來解決優化問題已不可能。一種較為成功的方法是通過將計算資源與特性集匹配來實現。將一種復雜系統映射到硅中,在相當程度上依賴于設計是在現有SoC上實現還是從頭做起。對于前一種情況,系統設計師應從了解四個

關鍵字:

TI SoC ASIC

利用嵌入式硅IP可以縮短SoC設計所需的開發時間,這已成為眾所公認的事實。但要從完工后的整個系統角度出發,整合及驗證來自多家廠商的元件,需要相當的時間和努力,然而它們卻常被忽略。這會對嵌入式軟件開發人員造成額外負擔,因為他們需要SoC的外圍和接口以及處理器的精確模型,才能在設計投片之前,針對正在開發的SoC,迅速完成應用固件的測試及除錯。如果SoC平臺以可配置處理器和外圍IP為基礎,這些IP又來自多家供貨商,這種情形就更加重要,因為設計人員必須確認在特定配置下,每個元件的功能不會影響到其它元件的工作。除此

關鍵字:

ARC SoC ASIC

摘 要:AMBA總線是目前主流的片上總線。本文給出的雙層AMBA總線設計能極大地提高總線帶寬,并使系統架構更為靈活。文章詳細介紹了此設計的實現,并從兩個方面對兩種總線方式進行了比較。關鍵詞:雙層AMBA總線;總線帶寬;SoC

引言一般說來,SoC芯片是由片上芯核、用戶設計的IP核以及將這兩者集成在一起的總線組成的。片上芯核決定了使用何種片上總線以及芯片的體系結構。ARM系列嵌入式微處理器憑借其高性能、低功耗的特點占據了市場的主要份額,ARM7TDMI因其相對低廉的價格

關鍵字:

SoC 雙層AMBA總線 總線帶寬 SoC ASIC

賽普拉斯半導體公司的子公司——賽普拉斯微系統公司 (Cypress MicroSystems) 近日宣布:其體積最小、集成度最高的可編程系統級芯片 (PSoCTM) 混合信號陣列已進入批量生產銷售階段。除了4個可配置模擬部件和4個可配置數字部件之外,CY8C21x34器件還提供了用于程序存儲器的8K字節快閃存儲器和用于數據存儲的512字節SRAM,從而使其成為對成本敏感的消費類和工業控制應用(比如觸摸感應控制屏、安全傳感器和控制、智能型溫度、壓力和流量傳感器、大型傳感器陣列、風扇控制器和電池充電器等)的理

關鍵字:

Cypress SoC ASIC

摘 要:本文介紹了IP核的概念及其在SoC設計中的應用,討論了為提高IP核的復用能力而采用的IP核與系統的接口技術。 關鍵詞:SoC;IP核;OCP引言隨著半導體技術的發展,深亞微米工藝加工技術允許開發上百萬門級的單芯片,已能夠將系統級設計集成到單個芯片中即實現片上系統SoC。IP核的復用是SoC設計的關鍵,但困難在于缺乏IP核與系統的接口標準,因此,開發統一的IP核接口標準對提高IP核的復用意義重大。本文簡單介紹IP核概念,然后從接口標準的角度討論在SoC設計中提高I

關鍵字:

IP核 OCP SoC SoC ASIC

中國每三年舉辦一次的固態和集成電路技術國際會議(International Conference on Solid-State and Integrated-Circuit Technology,ICSICT)是目前在中國召開的集成電路和微電子技術領域最高級別和最大的國際會議。它提供了一個展示固態和集成電路領域最新發展的國際交流平臺,為提高中國集成電路技術的學術水平和推動中國集成電路產業的發展起到了十分積極的作用。固態器件、集成電路、工藝技術、先進材料和其它相關的所有研究領域都屬于會議的討論范圍。&nbs

關鍵字:

Cadence SoC ASIC

嵌入式標準產品(ESPs)的先驅企業QuickLogic公司(Nasdaq股票代碼: QUIK)于今天日發布了QL92xxx 系列可編程片上系統器件(ProgrammableSOC)的。該系列產品系列以廣受歡迎的以QuickMIPS 產品系列中的的QL902M為 為基礎并,內置了了專為用于嵌入式數字媒體應用的器件而設計的附加預編程模塊。該系列的首款產品為QL92010,其中內置了了一個IDE控制器。秉承QuickLogic一貫專注努力于提供有線/無線IP網絡數字媒體傳輸和處理的芯片解決方案的傳統,Quic

關鍵字:

QuickLogic SoC ASIC

2004年6月A版

摘 要:本文分析了深亞微米下超大規模SoC的電源設計中存在的問題,給出了業界適用的設計、驗證方法,并以工程設計為例,給出層次性SoC設計中電源設計、驗證的適用流程。

關鍵詞:系統芯片;電源電壓降;地電壓反彈;電源網格

引言

SoC(系統芯片)是現代微電子技術向前發展的必然趨勢。與工藝技術逐步先進的變化相適應,SoC芯片上的內核邏輯的供電電壓也逐步降低。供電電源電壓減小的一個顯著好處是使整個芯片的功耗降低,然而它同時也帶來了芯片噪聲容限降低的負面影響。芯片供電電源

關鍵字:

SoC SoC ASIC

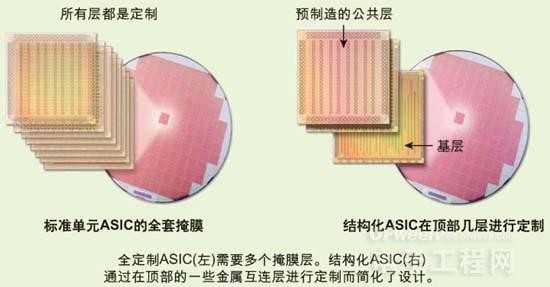

電子設計應用2004年第9期 門陣列的好處在于它不僅可以減小PCB板的尺寸,而且可以降低功耗、提高可靠性,以及降低整個系統成本。但由于門陣列的設計工具價格太高, 流片費用(NRE)的負擔太重,風險高,設計周期太長, 所以不能被一般公司所采用。Xilinx開發出的第一批基于SRAM的FPGA, 由于其軟件價格很低,沒有流片費用,所以它比門陣列更容易普及而被工程師所采用。如今芯片產業已經可以把數百萬門的邏輯放入一個芯片里,使其達到可以把整個系統濃縮到單個芯片的程度,這不僅代表把邏輯和ASIC 放入單一芯片,它

關鍵字:

FPSLIC SoC ASIC

賽普拉斯半導體公司 (NYSE:CY) 的子公司賽普拉斯微系統有限公司(Cypress MicroSystems)于今日宣布已開始生產一款新型可編程系統級芯片(PSoCTM)混合信號陣列。這種具有擴展數字集成功能的新型器件拓展了廣受歡迎的PSoC架構的適用范圍,以滿足消費類、工業、辦公自動化、電信和汽車應用中更大規模、更復雜的嵌入式控制功能的需要。賽普拉斯微系統公司的市場副總裁John McDonald說:“我們注意到客戶需要更多的數字功能,以提高外圍部件的集成度。我們的新款PSoC器件使得可用于實現片上

關鍵字:

賽普拉斯 SoC ASIC

日前,Mentor和華為共同宣布共同建立SOC軟硬件協同驗證環境。旨在加強SoC驗證方面雙方的全面合作。事先,華為已經利用Mentor公司提供的Seamless軟硬件協同驗證方案成功建立了ARM-based SoC驗證環境。利用Seamless協同驗證環境,華為已經成功調試,并解決了多款基于ARM7TDMI、 ARM926ejs、Power PC的SoC芯片軟硬件接口問題。華為早在上個世紀90年代就認識到SoC的功能驗證比傳統的ASIC的功能驗證更具有挑戰性,需要付出更多的仿真努力,同時產品的開發周期也更

關鍵字:

Mentor Graphics SoC ASIC

smic-asic介紹

您好,目前還沒有人創建詞條smic-asic!

歡迎您創建該詞條,闡述對smic-asic的理解,并與今后在此搜索smic-asic的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473