smic-asic 文章 最新資訊

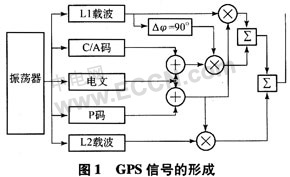

基于軟件的GPS接收機本地系統(tǒng)

- 0引言 對于一個普通的GPS(全球定位系統(tǒng))接收機來說,其對信號的捕獲和追蹤均由硬件進行處理,主要是用ASIC(專用集成電路)實現(xiàn)。用ASIC的主要好處之一是它的有效性,能夠?qū)PS信號進行有效處理,但它的造價較高,而目前GPS技術(shù)還在高速發(fā)展,各種算法還在不斷研究,如果都用ASIC來實現(xiàn),顯然并不現(xiàn)實。而使用軟件來模擬搭建GPS的接收系統(tǒng),不但可以方便地對現(xiàn)有的一些算法進行比較,而且也能快速地應(yīng)用到實際中。在該系統(tǒng)中,用A/D轉(zhuǎn)換器將輸入的模擬信號數(shù)字化,然后交由軟件接收機處理,由此重構(gòu)的系統(tǒng)

- 關(guān)鍵字: GPS ASIC A/D轉(zhuǎn)換器 MATLAB

Catalyst新型5通道電壓監(jiān)控器降低系統(tǒng)成本節(jié)約板基空間

- Catalyst半導(dǎo)體繼續(xù)快速擴展電壓監(jiān)控產(chǎn)品線,為微處理器、微控制器,ASIC器件和其它系統(tǒng)處理器的應(yīng)用新增一款高精度超低功耗5通道監(jiān)控器件。5通道電壓監(jiān)控被整合于一個小尺寸的8引腳MSOP封裝之內(nèi),CAT885能有效降低系統(tǒng)成本、節(jié)約電路板空間。 CAT885具備低有效漏極開路輸出及手動復(fù)位輸入的特點,可針對各種電子產(chǎn)品完成系統(tǒng)復(fù)位和監(jiān)控功能。CAT885可以監(jiān)控多達5通道的系統(tǒng)電壓,若所有被監(jiān)控的電源電壓已經(jīng)超過額定電平值,并且隨后被啟動的器件內(nèi)部計時器超時溢出后,有效的復(fù)位輸出才會終止,

- 關(guān)鍵字: Catalyst 電壓監(jiān)控器 微處理器 微控制器 ASIC

采用DSP、PLD和ASIC實現(xiàn)多速濾波器設(shè)計的比較

- 許多通信系統(tǒng)都要用到多速濾波器(multirate filter),多速濾波器是指輸出數(shù)據(jù)速率與輸入數(shù)據(jù)速率不相等的濾波器,常用于某個物理接口如數(shù)模轉(zhuǎn)換器(DAC)或模數(shù)轉(zhuǎn)換器(ADC)的接口處。

- 關(guān)鍵字: ASIC DSP PLD 濾波器設(shè)計

VERISILICON加盟“功耗前鋒倡議”加速高級低功耗設(shè)計

- 世界級ASIC設(shè)計晶圓廠及定制解決方案供應(yīng)商VeriSilicon Holdings Co., Ltd.(VeriSilicon)“已經(jīng)加盟功耗前鋒倡議”( Power Forward Initiative,PFI),計劃為其ASIC客戶提供基于通用功率格式(Common Power Format,CPF)的設(shè)計解決方案。 VeriSilicon采用Cadence低功耗解決方案,是業(yè)界領(lǐng)先的完整的設(shè)計流程,以Si2標準的CPF為基礎(chǔ),貫穿邏輯設(shè)計、驗證、實現(xiàn)等技術(shù)。這種針

- 關(guān)鍵字: 晶圓 VeriSilicon ASIC 低功耗 CPF

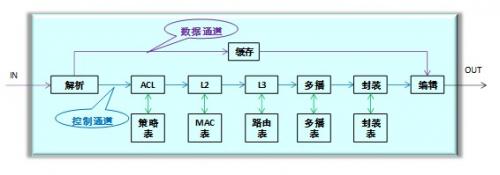

以高性能匯聚平臺 迎接視頻監(jiān)控新挑戰(zhàn)

- 隨著人們對安全需求的日益重視和性能的不斷增強、價格的迅速降低,應(yīng)用市場正快速膨脹。但是不管是定位于中小企業(yè)、中小網(wǎng)絡(luò)的DVR解決方案,還是定位在高端、企業(yè)級用戶的DVS,以及廣被業(yè)界看好的IP攝像機,都對方案提供商提出了更高的要求(更多挑戰(zhàn)):更高的視頻信號分辨率和壓縮比;更靈活的媒體格式支持;更安全的內(nèi)容保護;更低的功耗、成本和開發(fā)復(fù)雜度。 在視頻監(jiān)控應(yīng)用領(lǐng)域主要包括媒體處理器、DSC、ASIC、以及FPGA等幾種方案。其中DSC雖然具有部分DSP的功能,但是從總體來講,DSC和媒體處理器一樣

- 關(guān)鍵字: 視頻監(jiān)控 DVS DSC ASIC

針對未來的任務(wù)關(guān)鍵設(shè)計應(yīng)采用那種耐輻射平臺?(06-100)

- 暴露在惡劣的太空環(huán)境下的系統(tǒng)必須能在各種極端的條件下正常工作,且不喪失任何功能。太空系統(tǒng)在其生命期內(nèi)采集的信息若有任何微小偏差,都可能會對整個數(shù)據(jù)作出錯誤的詮釋。由于這些太空系統(tǒng)都是執(zhí)行特別重要任務(wù)的系統(tǒng),在設(shè)計時就必須考慮多個因素,除了功耗、系統(tǒng)重量、體積和發(fā)射時間等因素外,系統(tǒng)的可靠性是最主要關(guān)鍵。例如,執(zhí)行太空任務(wù)的衛(wèi)星必須能夠在整個生命期內(nèi) (通常是數(shù)十年) 耐受各種惡劣的環(huán)境條件。就可靠性而言,在太空運行的系統(tǒng)面臨最大的挑戰(zhàn)也許是持續(xù)的輻射轟擊。提高系統(tǒng)的耐輻射能力正迅速成為系統(tǒng)工程師的一項

- 關(guān)鍵字: Actel FPGA 耐輻射 RH-ASIC

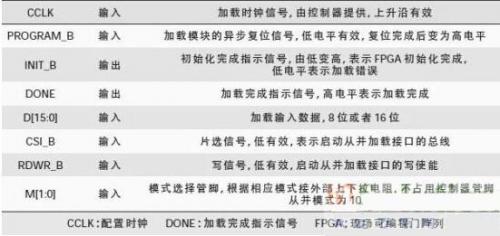

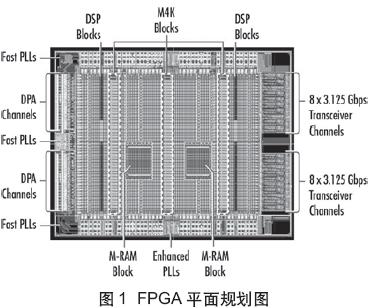

在FPGA中集成高速串行收發(fā)器面臨的挑戰(zhàn)(04-100)

- Altera公司對PCI Express,串行Rapid I/O和SerialLite等串行標準和協(xié)議的認可,將促進具有時鐘和數(shù)據(jù)恢復(fù)(CDR)功能的高速串行收發(fā)器的應(yīng)用。這些曾在4或8位ASSP中使用的收發(fā)器現(xiàn)在可以集成在高端FPGA中。帶有嵌入式收發(fā)器的FPGA占據(jù)更小的電路板空間,具有更高的靈活性和無需接口處理的兩芯片方案等優(yōu)勢,因此,采用這種FPGA對電路板設(shè)計者是很具有吸引力的選擇。 在FPGA中集成收發(fā)器使得接口電路處理工作由電路板設(shè)計者轉(zhuǎn)向芯片設(shè)計者。本文闡述在一個FPGA中集成1

- 關(guān)鍵字: Altera FPGA ASSP ASIC

紅外動目標識別跟蹤系統(tǒng)的DSP+FPGA實現(xiàn)

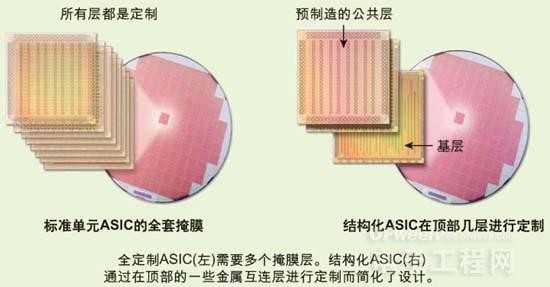

- 與通用集成電路相比,ASIC芯片具有體積小、重量輕、功耗低、可靠性高等幾個方面的優(yōu)勢,而且在大批量應(yīng)用時,可降低成本。現(xiàn)場可編程門陣列(FPGA)是在專用ASIC的基礎(chǔ)上發(fā)展出來的,它克服了專用ASIC不夠靈活的缺點。與其他中小規(guī)模集成電路相比,其優(yōu)點主要在于它有很強的靈活性,即其內(nèi)部的具體邏輯功能可以根據(jù)需要配置,對電路的修改和維護很方便。DSP+FPGA結(jié)構(gòu)最大的特點是結(jié)構(gòu)靈活,有較強的通用性,適于模塊化設(shè)計,從而能夠提高算法效率;同時其開發(fā)周期較短,系統(tǒng)易于維護和擴展,適合于實時數(shù)字信號處理。本

- 關(guān)鍵字: ASIC

PLD公司三極化形成

- 可編程邏輯器件(PLD)在與ASIC之激戰(zhàn)中已經(jīng)告捷:每年開始PLD設(shè)計的項目數(shù)目遠遠高于ASIC項目開工數(shù)。同時,PLD廠家之間也發(fā)生微妙的變化,由崛起時的爭強好斗和互不相讓,漸漸找到了各自的落腳點。目前看來,Xilinx的產(chǎn)品穩(wěn)居65nm FPGA市場,Altera最大的量產(chǎn)在90nm FPGA,Actel憑低功耗0.13微米FPGA在對功耗要求苛刻的領(lǐng)域站穩(wěn)了腳跟。昔日的兩個龐然大物——Xilinx和Altera之間拉開了距離,同時小型FPGA廠商如Actel躍躍欲試,漸漸跳

- 關(guān)鍵字: PLD FPGA ASIC

提高ASIC驗證的速度與可視性

- 前言 高性能、高容量FPGA在ASIC/SoC原型設(shè)計及系統(tǒng)兩方面的應(yīng)用持續(xù)增長。這些設(shè)計通常包括硬件及嵌入式軟件(也可能包括應(yīng)用軟件)的復(fù)雜組合,這給系統(tǒng)驗證帶來了巨大負擔(dān),原因是檢測、隔離、調(diào)試及校正故障要比最初設(shè)計所花費的時間、資金和工程資源多得多。 由于軟硬件之間交互作用相當(dāng)復(fù)雜且無法預(yù)見,僅僅是找到深藏于系統(tǒng)中的故障就需要進行長時間的測試序列,而且隨后的調(diào)試過程還需要花費更多的時間及精力。另外,如果驗證測試使用視頻流等實際數(shù)據(jù)時,那么間發(fā)故障將很難(如果并非不可能)重現(xiàn)。

- 關(guān)鍵字: FPGA ASIC 模擬器

Xilinx開放源碼硬件創(chuàng)新大賽復(fù)賽名單公布

- 2008年1月8日,北京訊:自2007年6月正式開始的覆蓋全國高校的“中國電子學(xué)會Xilinx開放源碼硬件創(chuàng)新大賽”初賽經(jīng)過大賽組委會的認真篩選,來自34所高校的53支隊伍從170多支參賽隊伍中脫穎而出,入圍復(fù)賽階段。入圍隊伍中,大連理工,清華,電子科大, 西安電子科大等表現(xiàn)突出, 僅大連理工就有6支隊伍進入復(fù)賽。 開賽以來,包括清華、北大、中國電子科技大學(xué)、西安電子科技大學(xué)、中國科技大學(xué)等在內(nèi)的近50所高校學(xué)生踴躍報名, 共有170多只隊伍的1000多位在校

- 關(guān)鍵字: Xilinx 開放源碼硬件創(chuàng)新大賽 入圍 復(fù)賽 模擬技術(shù) 電源技術(shù) SoC ASIC

電壓調(diào)節(jié)技術(shù)用于SoC低功耗設(shè)計

- 引言 SoC即“System on chip”,通俗講為“芯片上的系統(tǒng)”,主要用于便攜式和民用的消費的電子產(chǎn)品。隨著便攜式和民用電子產(chǎn)品的高速發(fā)展,廣大用戶對便攜設(shè)備新功能的要求永無止境。于是要求設(shè)計人員在設(shè)計小型便攜式消費類電子產(chǎn)品時,不僅要縮小產(chǎn)品尺寸、降低成本,更重要的是降低功耗,用戶都希望便攜式產(chǎn)品的電池充電后的工作時間越長越好。于是,系統(tǒng)設(shè)計與SoC 設(shè)計人員面臨著在增加功能的同時保證電池的使用時間的挑戰(zhàn)。要達到這一點,就需要使用新的節(jié)能技術(shù),比如電壓調(diào)節(jié)(voltage scalin

- 關(guān)鍵字: SoC 芯片 電壓調(diào)節(jié) SoC ASIC

smic-asic介紹

您好,目前還沒有人創(chuàng)建詞條smic-asic!

歡迎您創(chuàng)建該詞條,闡述對smic-asic的理解,并與今后在此搜索smic-asic的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對smic-asic的理解,并與今后在此搜索smic-asic的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司