在FPGA中集成高速串行收發(fā)器面臨的挑戰(zhàn)(04-100)

Altera公司對PCI Express,串行Rapid I/O和SerialLite等串行標準和協(xié)議的認可,將促進具有時鐘和數(shù)據(jù)恢復(fù)(CDR)功能的高速串行收發(fā)器的應(yīng)用。這些曾在4或8位ASSP中使用的收發(fā)器現(xiàn)在可以集成在高端FPGA中。帶有嵌入式收發(fā)器的FPGA占據(jù)更小的電路板空間,具有更高的靈活性和無需接口處理的兩芯片方案等優(yōu)勢,因此,采用這種FPGA對電路板設(shè)計者是很具有吸引力的選擇。

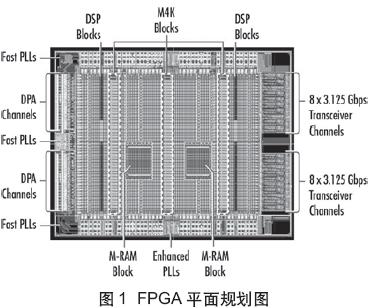

本文引用地址:http://www.104case.com/article/80879.htm在FPGA中集成收發(fā)器使得接口電路處理工作由電路板設(shè)計者轉(zhuǎn)向芯片設(shè)計者。本文闡述在一個FPGA中集成16×3.125Gbps高速收發(fā)器所面臨的挑戰(zhàn),其主要難點包括以下四個方面:平面規(guī)劃,設(shè)計方法,布版和封裝。

平面規(guī)劃

設(shè)計兩個不同的FPGA派生平面規(guī)劃:一個沒有收發(fā)器,一個具有收發(fā)器。首先設(shè)計第一個沒有收發(fā)器的器件。當需要設(shè)計具有收發(fā)器的器件時,我們重新利用第一個器件80%的平面規(guī)劃,將其右側(cè)的LVDS I/O模塊去掉,代之以收發(fā)器模塊(參見圖1)。為了減小失誤,我們先對一個具有全部功能的測試芯片進行收發(fā)器設(shè)計驗證。當收發(fā)器設(shè)計實現(xiàn)了性能提高時,再將16個收發(fā)器模塊全部集成到器件中去。

另一個難點是對晶片上高速收發(fā)器通道上的信號完整性進行優(yōu)化。首選是最短通道。收發(fā)器I/O同晶片表面的針腳矩陣進行縱向連接,以避開幾個中間的金屬連接層。收發(fā)器模塊中的金屬層必須手工布線,以便于縱向連接布線。該FPGA采用TSMC的0.13mm工藝設(shè)計。

評論