怎樣為定時應用選擇合適的采用PLL的振蕩器

十幾年前,頻率控制行業推出了基于鎖相環(PLL)的振蕩器,這是一項開拓性創新技術,采用了傳統晶體振蕩器(XO)所沒有的多項特性。憑借內部時鐘合成器IC技術,基于PLL的XO可編程來支持更寬廣的頻率范圍。這一突破消除了為在特定頻率實現共振而切割和加工石英所需的材料加工工藝步驟。這一創 新也使得對基于PLL的XO進行頻率編程成為可能并且實現極短交貨周期。

鑒于傳統振蕩器交貨周期可能接近14周或更長,許多硬件設計人員渴 望利用可編程振蕩器獲得顯著的交貨周期優勢。不幸的是,嚴重的問題發生了。一些已經從傳統XO遷移到基于PLL的XO的設計陷入了關聯抖動 (jitter-related)問題之中,這會引起關聯應用(application-related)失效,涉及范圍從通信鏈路中的超高位錯誤率到無 法工作的SoC和處理器。這些問題迫使許多IC供應商規定:基于PLL的振蕩器不能和他們的器件配合使用。這種形勢的變化使得想通過基于PLL的振蕩器獲 得頻率靈活性和短交付周期優勢的硬件工程師面臨挑戰。

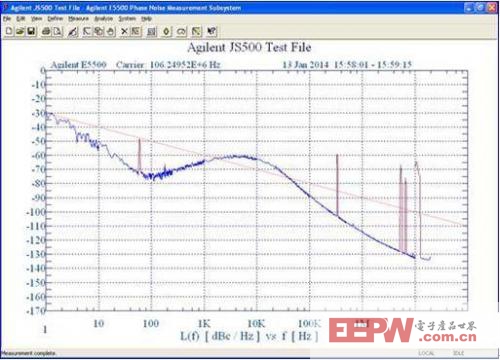

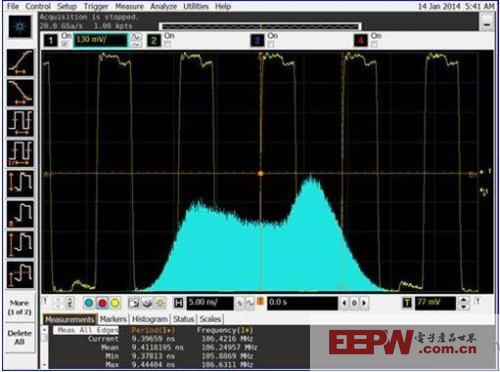

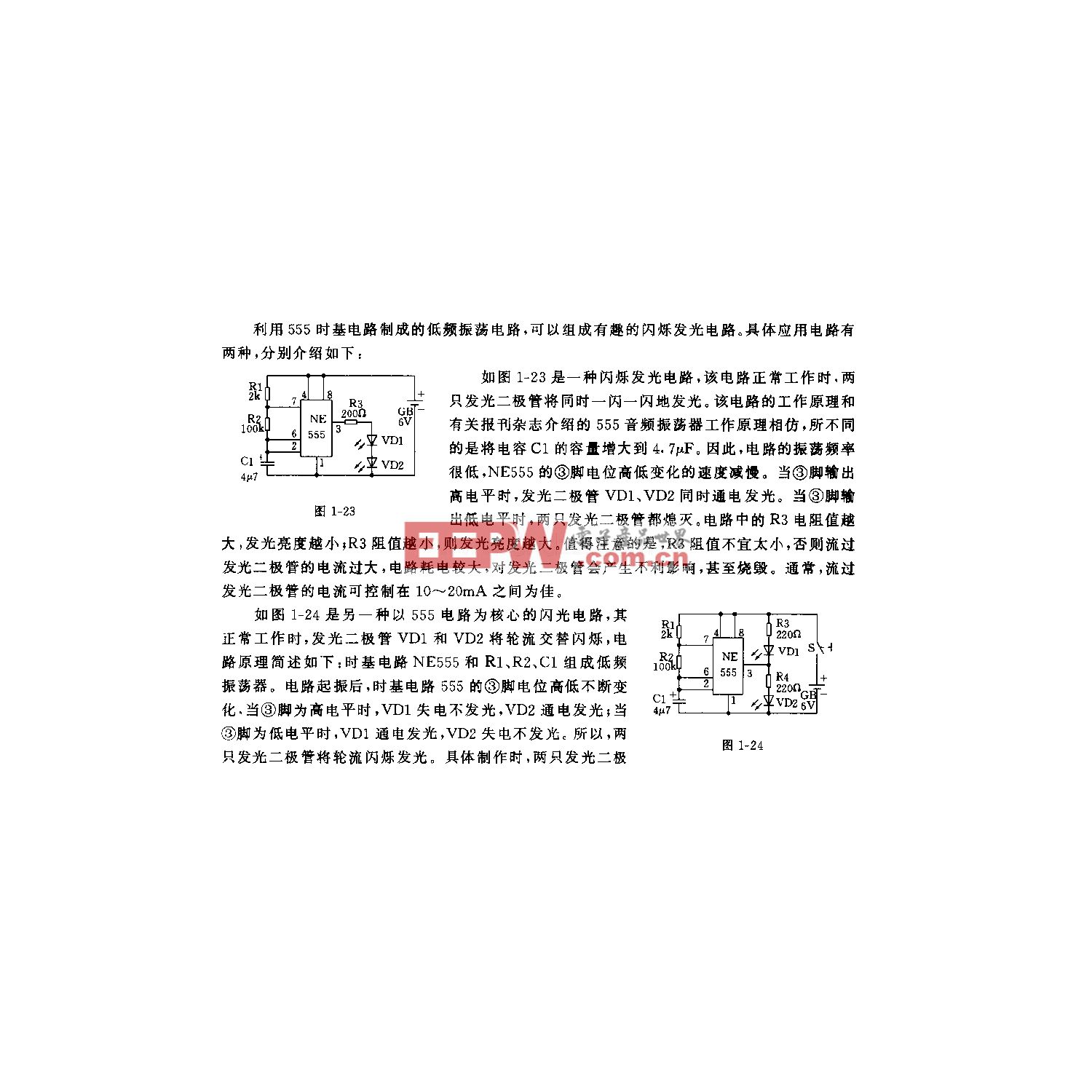

為什么會出現這種情況?其原因在于來自不同供應商的PLL技術差異極大。不合格的 PLL設計導致過多的振蕩器相位噪聲和抖動峰值,如圖1中左側畫面所示。這個特定的基于PLL的XO在12kHz-20MHz帶寬上的相位抖動為 150ps RMS。這種性能水平使它不適合為高速PHY提供時鐘,高速PHY通常需要1ps RMS 抖動的參考時鐘。XO的周期抖動在圖1右側圖片中有顯示。這種雙峰周期抖動可能是一個出現PLL穩定性問題的信號,PLL穩定性能夠對使用這個XO的 SoC產生有害的性能影響。與可編程振蕩器展現抖動峰值有關的第二個領域是級聯PLL。當這樣一個基于PLL的振蕩器被連接到一個后續電路中帶有PLL的 IC上時,抖動可能會增加。

圖1–不合格的基于PLL的XO設計導致過多的相位噪聲和周期抖動

好消息是并非所有的PLL,確切的說不是所有基于PLL的振蕩器,都是一樣的。通過特有的PLL設計技術,可編程振蕩器能夠提供可媲美一流石英振蕩器的抖動 性能,同時克服級聯PLL帶來的問題。這些高性能的基于PLL的振蕩器能夠用于處理器/SoC時鐘,以及高速串行器、PHY和FPGA時鐘。

開發人員可以使用三個簡單的標準來評價基于PLL的XO能否被用于給定的應用。

抖 動生成—在級聯的PLL應用(例如FPGA和PHY時鐘),XO參考時鐘抖動與FPGA/PHY內部PLL抖動相混合。采用低抖動XO參考時鐘(例 如1ps RMS相位抖動)可以最大化可容許的FPGA/PHY內部PLL所產生的抖動值,最大化整體設計的抖動余量。

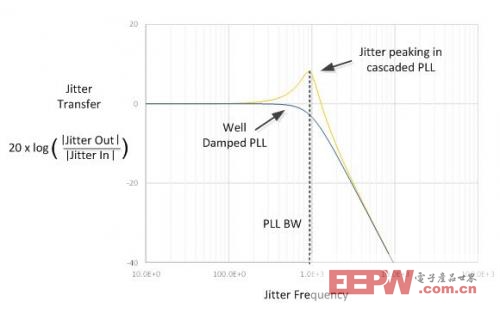

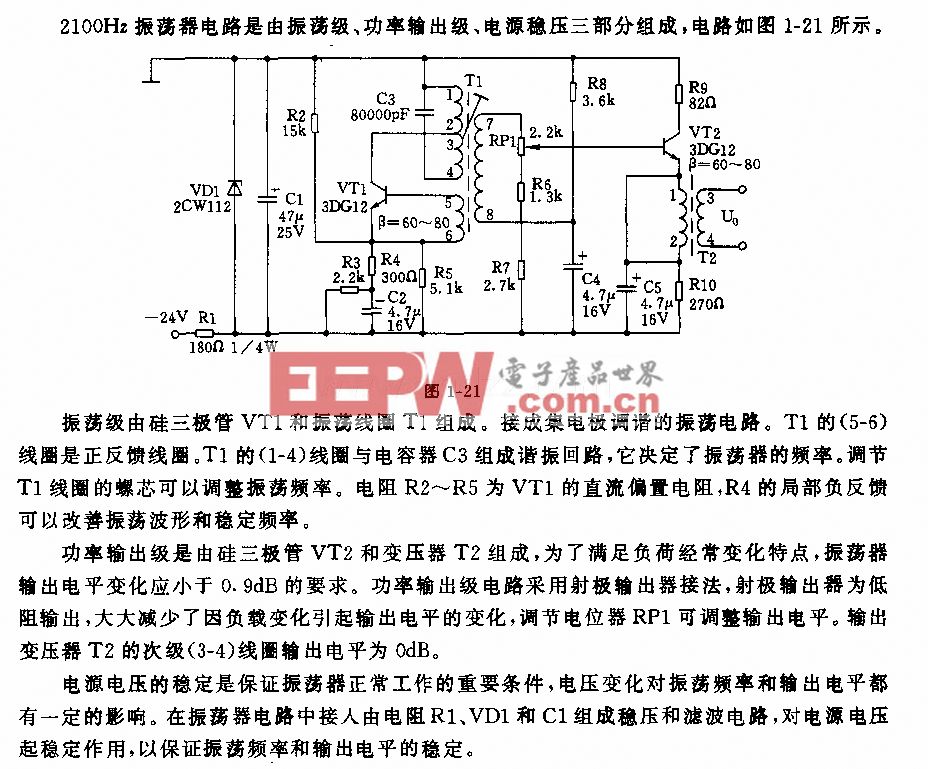

抖動峰值—當第一級和第二級PLL的環路帶寬相同時,級聯PLL存在過大抖動的風險。這種風險很容易通過使用一個具有相對較低內部PLL帶寬的基于PLL的 振蕩器進行緩解。PLL應當得到很好的抑制,以確保不超過1%的峰值(0.1db),如圖2所示。通用soc>1MHz。使用具有低抖動峰 值和極低內部帶寬的基于PLL的振蕩器確保它的峰值不會與下游PLL的帶寬重疊。這種架構使得第二級PLL容易的跟蹤第一級PLL的變化,同時維持可接受 的環路穩定性和相位余量。

圖2-基于PLL的抖動跟蹤和過濾有助于減輕抖動峰值

評論