- 本文給出了一種簡單的模型,可用來在PLL系統中準確地預測由于充電泵和/或運算放大器泄漏電流引起的基準雜散噪聲的大小。知道如何預測這類噪聲有助于在PLL系統設計的早期明智地選擇環路參數。

- 關鍵字:

PLL VCO IC

- 大部分電路板設計人員知道時鐘組件選擇并不簡單。好在設計并提供時序組件的大公司認識到客戶面臨的這一問題,提供工具支持設計人員迅速完成時鐘樹,并不要求設計人員是模擬設計PhD。讓我們看一下目前選擇并設計時鐘組件所需要處理的某些問題,討論完成每一項工作需要哪些幫助。在電路板設計流程中,時鐘提供服務功能以滿足體系結構構建模塊的要求。在選擇這些體系結構組件之前,還無法確定所有的時鐘規范。注意,某些復雜的通信系統的確解決了體系結構的一些時序功能問題,例如,網絡同步等。選擇了體系結構單元后,電路板設計人員應注意電源

- 關鍵字:

電路板 LED IDT PLL

- 電子產品世界,為電子工程師提供全面的電子產品信息和行業解決方案,是電子工程師的技術中心和交流中心,是電子產品的市場中心,EEPW 20年的品牌歷史,是電子工程師的網絡家園

- 關鍵字:

PLL 射頻前端 接收機 LNA 鎖相環

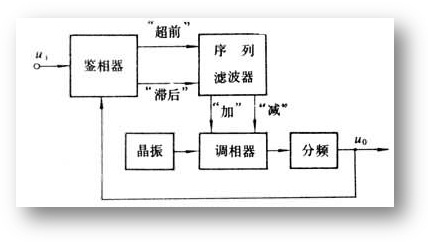

- STM32F系列微處理器,或者說是Cortex-M3內核的MCU內,都集成了一個叫PLL的東西。PLL就是鎖相回路或鎖相環(Phase Locked Loop),用來統一整合時脈訊號,使內存能正確的存取資料。PLL用于振蕩器中的反饋技術,將外部的輸入信號與內部的振蕩信號同步,鎖相環路的基本方框圖如下圖所示。一句話,PLL用來控制STM32F的時鐘頻率的。總而言之,STM32F系列MCU使用了這個東西,而我們在MCU上電之后,也就要對其正確的初始化,這樣,我們才能得到我們需要的時鐘配置。

- 關鍵字:

微處理器 STM32F PLL MCU 時鐘

- 所有的數字電路都需要依靠時鐘信號來使組件的運作同步,每單位時間內電路可運作的次數取決于時鐘的頻率,因此時 ...

- 關鍵字:

可編程時鐘 時鐘發生器 PLL

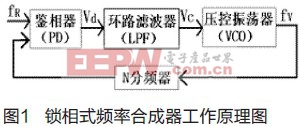

- 摘要:介紹了一種P波段可控頻率源的設計方案和相關理論,采用PLL即鎖相技術實現P波段的頻率產生,具有相位噪聲低,雜散低的特點。利用單片機作為數據處理核心對鎖相環的鑒相器進行置數和控制,實現了480~540MHz、步進為1MHz的可控頻率輸出。

- 關鍵字:

P波段 可控頻率源 PLL 鑒相器 單片機 201309

- Mouser Electronics備貨由Analog Devices推出的業界最高頻率PLL合成器。 ADI ADF41020微波PLL合成器旨在改善下一代無線電設計的性能,同時大幅減少元件數量并降低系統成本。

- 關鍵字:

ADI Mouser ADF41020 PLL

- 鎖相環(PLL)頻率合成器中的電荷泵電壓用于控制VCO的振蕩頻率。大多數PLL的電荷泵電壓一般為5V或6V,因而電荷泵電壓可控的VCO頻率調諧范圍和調諧精度都是有限的。ADI公司推出帶高電壓電荷泵的PLL頻率合成器ADF4113HV

- 關鍵字:

合成器 設計 頻率 PLL 電壓 電荷 基于

- 與石英晶體振蕩器等效的頻率穩定的1~399KHZ PLL合成振蕩電路電路的功能如果要求振蕩頻率準確、穩定度好, ...

- 關鍵字:

石英晶體 振蕩器 頻率穩定 PLL

- 不管是放到測試設置中,還是作為被測設備的一部分,時鐘恢復都在進行準確的測試測量時發揮著重要作用。由于大多數千兆位通信系統都是同步系統,因此系統內部的數據都使用公共時鐘定時。不管是沿著幾英寸的電路板傳送

- 關鍵字:

PLL 時鐘恢復 設計方案

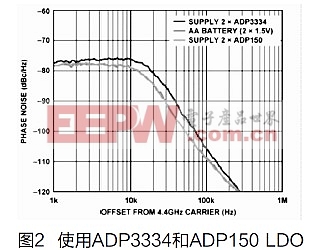

- 摘要:鎖相環是現代通信系統的基本構建模塊,而電源噪聲越來越影響鎖相環性能。本文通過列舉多種電源管理電路設計的新方法,解析不同的設計對鎖相環性能產生的影響。

- 關鍵字:

VCO PLL 201209

- 在非相參雷達測試系統中,頻率合成技術是其中的關鍵技術之一,它要求在一個很寬的頻率范圍內以快捷的速度,提供大...

- 關鍵字:

PLL 低相位噪聲 環路濾波器

- XC25BS7系列是內置分頻,倍頻電路,在整個頻率范圍內保持低消耗電流,具有超小型封裝的PLL時鐘發生器IC。輸...

- 關鍵字:

PLL 時鐘發生器 XC25BS7

- 1 引言 本文在傳統鎖相環結構的基礎上進行改進,設計了一款用于多路輸出時鐘緩沖器中的鎖相環,其主 要結構包括分頻器、鑒頻鑒相器(PFD)、電荷泵、環路濾波器和壓控振蕩器(VCO)。在鑒相器前采用預 分頻結構減小時

- 關鍵字:

CSMC PLL 工藝 零延時

multi-pll介紹

您好,目前還沒有人創建詞條multi-pll!

歡迎您創建該詞條,闡述對multi-pll的理解,并與今后在此搜索multi-pll的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473