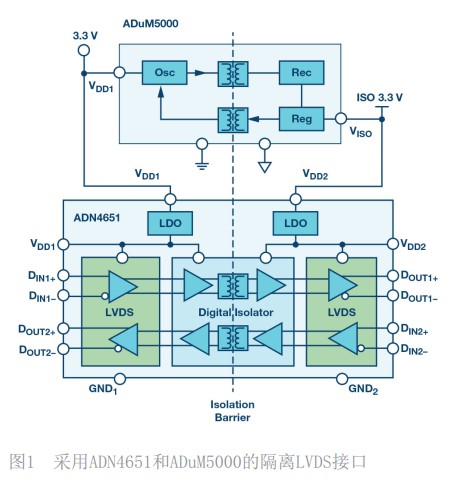

- 介紹了高速信號傳輸的挑戰,及ADI公司的信號隔離式LVDS緩沖器——ADN4650/ADN4651/ADN46521是,若與ADuM5000組合使用,可實現短距離600 Mbps和數米距離200 Mbps的傳輸速率。

- 關鍵字:

數字隔離 LVDS 接口 201902

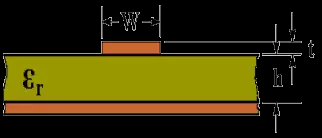

- 沒有阻抗控制的話,將引發相當大的信號反射和信號失真,導致設計失敗。常見的信號,如PCI總線、PCI-E總線、USB、以太網、DDR內存、LVDS信號等,均需要進行阻抗控制。阻抗控制最終需要通過PCB設計實現,對PCB板工藝也提出更高要求,經過與PCB廠的溝通,并結合EDA軟件的使用,按照信號完整性要求去控制走線的阻抗。 不同的走線方式都是可以通過計算得到對應的阻抗值。 微帶線(microstrip line) ?它由一根帶狀導線與地平面構成,中間是電介質。如果電介質的介電常數、線的寬度、及其與地

- 關鍵字:

PCB LVDS

- 據業內人士透露,三星電子幾乎訂購了中國LED外延片和芯片制造商三安光電位于廈門的Mini LED產能,以確保其將在2018年第三季度推出的大尺寸高端液晶電視背光芯片供應。

消息人士稱,三星已經為此次芯片供應預付了1683萬美元。

中國LED芯片制造商華燦光電和廈門乾照光電也已開始了MicroLED和Mini LED技術的研發,而中國的LED封裝服務提供商佛山國星光電則于2018年3月初設立了MicroLED和Mini LED研究中心,以便在2020年能夠封裝0.5-1.0mm的Mini

- 關鍵字:

三安光電 Mini LED

- 根據TrendForce光電研究最新“新型顯示技術成本”報告,由于Mini LED作為LCD背光的架構與現行LCD顯示器的LED背光架構相仿,在設計上并無太大改變,因此也被廠商寄予厚望,希望其可成為Micro LED量產前的過渡產品。但不論是手機或電視等消費性電子產品,Mini LED勢必將直接面對來自OLED的競爭,短期而言,大尺寸電視及高階IT產品是Mini LED有機會與OLED一較高下的應用領域。

以電視來看,WitsView指出,由于OLED的印刷上色技術尚未成

- 關鍵字:

Mini LED OLED

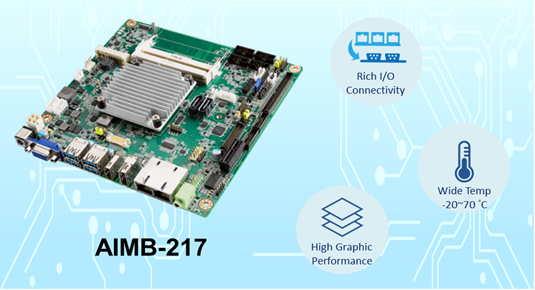

- 全球智能系統產業的領導廠商研華科技今天發布新型工業級無風扇超薄Mini-ITX主板AIMB-217。該產品搭載最新Intel? Pentium?、Celeron?和Atom? N4200/N3350/x7-E3950處理器(ATOM第六代Apollo Lake),相較于上一代產品而言CPU性能和顯示性能分別實現了30%和45%的顯著提升。同時,AIMB-217還捆綁研華專屬WISE-PaaS/RMM軟件套件,可實現遠程設備管理。 AIMB-217的顯示性能已提升

- 關鍵字:

研華 Mini-ITX

- 如何用單個賽靈思FPGA數字化數百個信號- 在新型賽靈思 FPGA 上使用低電壓差分信號(LVDS),只需一個電阻和一個電容就能夠數字化輸入信號。由于目前這一代賽靈思器件上提供有數百個 LVDS 輸入,理論上使用單個 FPGA 就能夠數字化數百個模擬信號。

- 關鍵字:

賽靈思 FPGA LVDS

- 數字電視的發展,使人們對各種高畫質影音設備的購買需求激增。FPD TV、DVD播放器、NB、數字相機及數字攝影機都已出現支持Full HD規格的產品。

- 關鍵字:

LCD LVDS IC

- 高速串行互連是標志并行數據總線向串行總線轉變的技術里程碑,這種技術是減少設計師面臨的信號阻塞問題的方法。這種轉變是由業界對系統成本和系統擴展能力的要求所推動的。隨著芯片技術的發展和芯片尺寸的縮小,用速率達數千兆位的高速串行互連來取代傳統的并行結構變得簡單易行。

- 關鍵字:

差分信號技術 LVDS FPGA

- 紅外成像導引頭采用紅外焦平面陣列探測器,易受太陽光等雜散光的影響,評估雜散光對紅外探測器成像質量的影響十分重要。由于導引頭輸出的信號一般采用LVDS或HOTLink格式傳輸,不能被雜散光測試設備直接接收,設計了一種圖像調理卡,采用FPGA為控制核心,將紅外探測器輸出的圖像信號進行格式轉換和調理后傳輸至雜散光測試設備。

- 關鍵字:

導引頭 LVDS FPGA

- JESD204B接口是一個串行解串器鏈路規范,允許12.5Gbps的最大數據速率傳輸。使用高級工藝(例如65nm或更小)的轉換器支持該最大數據速率,還可提高電源效率。系統設計人員可充分利用該技術相對于低壓差分信號(LVDS)DDR的優點

- 關鍵字:

數據轉換器 JESD204B LVDS PHY模式

- 摘要 網絡下載器作為航天計算機地面檢測系統的重要組成部分,發揮著重要的作用。文中主要介紹了網絡下栽器的總體設計思路,給出了硬件模塊的設計原理圖。并在PCB設計中,對于LVDS接口、高速總線以及疊層的設計中給出

- 關鍵字:

LVDS 通用下載器 FPGA

- 現場可編程門陣列(FPGA)與模數轉換器(ADC)輸出的接口是一項常見的工程設計挑戰。本文簡要介紹各種接口協議和標準,并提供有關在高速數據轉換器實現方案中使用LVDS的應用訣竅和技巧。接口方式和標準現場可編程門陣列

- 關鍵字:

FPGA ADC LVDS JESD204 接口方式

- 摘要:超高速ADC通常采用LVDS電平傳輸數據,高采樣率使輸出數據速率很高,達到百兆至吉赫茲量級,如何正確接收高速LVDS數據成為一個難點。本文以ADS42LB69芯片的數據接收為例,從信號傳輸和數據解碼兩方面,詳述了實

- 關鍵字:

LVDS ADC數據接收信號 完整性FPGA

mini-lvds介紹

您好,目前還沒有人創建詞條mini-lvds!

歡迎您創建該詞條,闡述對mini-lvds的理解,并與今后在此搜索mini-lvds的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473