如何用單個賽靈思FPGA數字化數百個信號

在新型賽靈思 FPGA 上使用低電壓差分信號(LVDS),只需一個電阻和一個電容就能夠數字化輸入信號。由于目前這一代賽靈思器件上提供有數百個 LVDS 輸入,理論上使用單個 FPGA 就能夠數字化數百個模擬信號。

本文引用地址:http://www.104case.com/article/201710/366427.htm我們團隊近期探索了可能的設計領域的一隅,對中心頻率為 3.75MHz 和精度為 5 位的有限帶寬輸入信號進行了數字化,同時還針對 128 元線性超聲陣列換能器的輸出信號研究了多種數字化方案。首先讓我們詳細介紹一下演示項目。

2009 年賽靈思推出了 LogiCORE™ 軟 IP 核。結合外置比較器、一個電阻和一個電容,就可實現一種能夠數字化頻率高達 1.205kHz[1] 輸入信號的模數轉換器(ADC)。

用 FPGA 的 LVDS 輸入取代外置比較器,同時結合使用增量調制器 ADC 架構,僅使用一個電阻和一個電容就能數字化頻率高得多的模擬輸入信號。

ADC 拓撲和實驗平臺

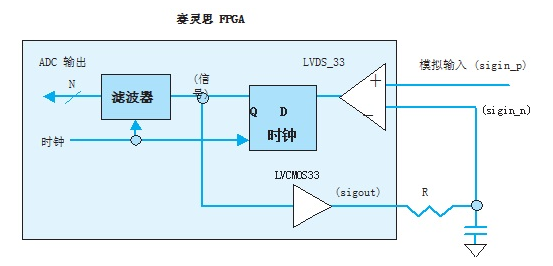

使用賽靈思 FPGA 上的 LVDS 輸入實現的單通道增量調制器 ADC[2]的方框圖見圖 1。這里模擬輸入驅動 LVDS_33 緩沖器非反相輸入,輸入信號范圍基本為 0-3.3V。以比模擬輸入信號頻率高得多的時鐘頻率對 LVDS_33 緩沖器輸出進行采樣并通過一個 LVCMOS33 輸出簡單而且所用元件數少,讓這個方法頗具吸引力。而且由于 LVDS_33 輸入緩沖器有相對較高的輸入阻抗,在許多應用中傳感器輸出可以直接連接到 FPGA 輸入,無需前置放大器或緩沖器。

緩沖器和一個外置一階 RC 濾波器反饋給 LVDS_33 緩沖器的反相輸入。采用這一電路,只要選擇合適的時鐘頻率 (F)、電阻 (R) 和電容 (C),反饋信號就會跟隨輸入模擬信號。

作為實例,圖 2 顯示的是在 F=240MHz、R=2K 和 C=47pF 時的輸入信號(黃色、通道 1)和反饋信號(藍色、通道2)。所示的輸入信號是用 Agilent 33250A 函數發生器使用其 200MHz、12 位任意輸出函數功能生成的。輸入信號的傅里葉轉換由小組使用的Tektronix DPO 3054 示波器計算完成,顯示為紅色(通道 M)。在這些頻率上,示波器探頭的輸入電容(以及接地問題)不會降低示波圖所顯示的反饋信號的質量,但圖 2 的確體現了該電路的運行情況。

通過對 1 Vpp 3.75MHz 正弦波運用布萊克曼–納托爾 (Blackman-Nuttall) 窗口,我們定義了圖 2 所示的有限帶寬輸入信號。雖然理論上窗口化信號的本底噪聲基本比中心頻率的幅度小 100dB,Agilent 33250A 函數發生器的采樣頻率和 12 位精度讓演示信號質量遠遜于理論水平。由于換能器的機械屬性,眾多超聲換能器產生的中心頻率接近 3.75MHz 的輸出信號自然是有限帶寬信號,因此對采用這種方法來說是理想的信號源。

圖 1 - 使用一個外部電阻和一個外部電容的單通道增量調制器 ADC。

圖 2 - 該示波圖所示的是 F=240MHz、R=2K 和 C=47pF 時 Agilent 33250A 函數發生器產生的 3.75 MHz 輸入信號(黃色,通道 1)和反饋信號(藍色,通道 2)。由 Tektronix DPO 3054 示波器計算完成的輸入信號傅里葉轉換顯示為紅色(通道 M)。

我們使用 Digilent Cmod S6 開發模塊[3]配合安裝在小型 PCB 上的賽靈思 Spartan®-6 XC6SLX4 FPGA,并使用 8 個RC 網絡和輸入連接器,讓圓形系統來同時數字化多達 8 路信號,即得到圖 2 所示的圖。每個通道并聯端接一個 50Ω 的接地電阻,以正確端接信號發生器的同軸電纜。需要注意的是為實現這樣的性能,我們小組將 LVCMOS33 緩沖器的驅動強度設置為 24mA,壓擺率設置為 FAST,如圖 5 中的實例 VHDL 源代碼中記錄的情況。

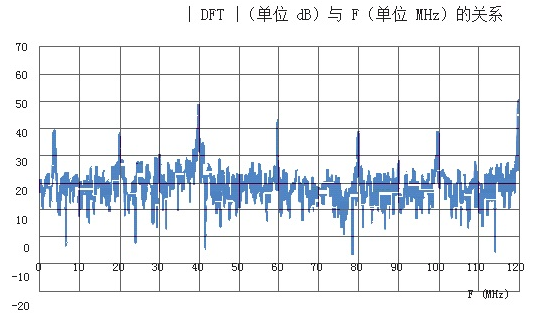

定制的原型電路板還支持使用 FTDI FT2232H USB 2.0 微型模塊[4],用于把數據包化的串行比特流傳輸到主機 PC 上供分析。圖 3 所示的是當饋給圖 2 的模擬信號時,原型電路板產生的比特流的傅里葉轉換幅度。與 240MHz 采樣頻率的分諧波有關的峰值清晰可見,另外還有與輸入信號相關的 3.75MHz 頻率下的峰值。

圖 3 - 本圖所示的是與圖 2 相關的配置產生的比特流的傅里葉轉換

大量抽頭

通過給比特流施加帶通有限脈沖響應 (FIR) 濾波器,就能夠產生模擬輸入信號的 N 位二進制表達:ADC 輸出。但是由于數字比特流的頻率遠遠高于模擬輸入信號,用戶需要使用帶有大量抽頭的 FIR 濾波器。不過由于被濾波的數據只有 0 和 1 兩個數值,所以無需使用乘法器(只需要加法器將 FIR 濾波器系數相加即可)。

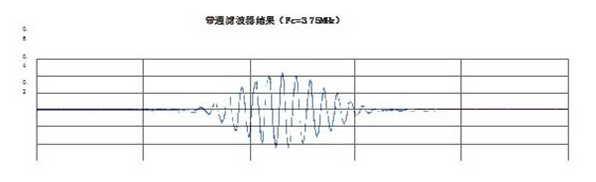

圖 4 - 使用中心頻率為 3.75MHz 的 801 抽頭帶通濾波器產生的 ADC 輸出。

圖 4 所示的 ADC 輸出是在主機 PC 上使用我們用免費在線 FIR 濾波器設計工具 TFilter[5]設計的中心頻率為3.75MHz 的 801 抽頭帶通濾波器產生的。該濾波器在 2.5MHz - 5MHz 通帶外的衰減率為 36dB 甚至更高,3MHz - 4.5MHz 之間的紋波為 0.58dB。

圖 4 所示的 ADC 輸出信號的精度大約為 5 位。這是最終的過采樣率的函數,用戶可以使用針對較低輸入頻率優化的設計來獲得更高精度。

圖 4 所示的 ADC 輸出信號在 240MHz 上也被嚴重地過采樣,可以大幅度縮小 ADC 輸出帶寬。在帶通濾波器和抽取模塊的硬件實現中,在通過抽取將有效采樣率降至 1/16 到 15MHz 時(比有限帶寬輸入信號的最高頻率快 3 倍),可以只計算第 16 個濾波器輸出值,從而降低硬件需求。

圖 5 所示的是與 Digilent Cmod S6 開發模塊結合使用,產生圖 2 所示的反饋信號以及與圖 3 的傅里葉轉換有關的比特流數據的 VHDL 源代碼。一個 LVDS_33 輸入緩沖器直接實例化

并分別連接到模擬輸入和反饋信號 sigin_p 和 sigin_n。內部信號 sig 由 LVDS_33 緩沖器的輸出驅動,并由內置的觸發器采樣,以產生 sigout。信號 sigout 是經濾波用于產生N位ADC輸出的串行比特流。我們使用免費的賽靈思 ISE® Webpack 工具實現該項目[6]。

VHDL 源代碼

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ; LIBRARY UNISIM ;

USE UNISIM.VCOMPONENTS.ALL ;

ENTITY deltasigma IS

PORT (clk :IN STD_LOGIC ;

sigin_p :IN STD_LOGIC ;

sigin_n :IN STD_LOGIC ;

sigout :OUT STD_LOGIC) ; END deltasigma ;

ARCHITECTURE XCellExample OF deltasigma IS SIGNAL sig :STD_LOGIC ;

BEGIN

myibufds:IBUFDS

GENERIC MAP (DIFF_TERM =》FALSE,

IBUF_LOW_PWR =》FALSE, IOSTANDARD =》 “DEFAULT”)

PORT MAP (O =》 sig,

I =》 sigin_p, IB =》 sigin_n);

mydeltasigma:PROCESS(clk) BEGIN

IF (clk = ‘1’ AND clk’EVENT) THEN

sigout 《= sig ; END IF ;

END PROCESS mydeltasigma ; END XCellExample ;

UCF文件

NET “clk” LOC = J1 |IOSTANDARD = LVCMOS33; NET “sigin_p” LOC = N12|IOSTANDARD = LVDS_33; NET “sigin_n” LOC = P12|IOSTANDARD = LVDS_33;

NET “sigout” LOC = P7 |IOSTANDARD = LVCMOS33| SLEW = FAST|DRIVE = 24;

圖 5 所示的是 VHDL 代碼和與圖 1 的電路相關的 UCF 文件部分。

減少元件數量

本文描述的 ADC 架構已經被近期發表的幾篇文章不準確地引用為德爾塔-西格瑪(ΔΣ)型架構[7]。雖然真正的ΔΣ型 ADC 有優勢,這種方法的簡便性和元件數少使之對部分應用有吸引力。而且由于 LVDS_33 輸入緩沖器有相對較高的輸入阻抗,在許多應用中傳感器輸出能夠直接連接到 FPGA 輸入,無需使用前置放大器或緩沖器。這在許多系統中都能體現出明顯的優勢。

本文方法的另一個優勢是通過疊加能夠“混合”多個串行比特流,使用單個濾波器就能恢復輸出信號。例如在基于陣列的超聲系統中,串行比特流可以延遲時間來實現聚焦算法,然后以向量方式相加,這樣使用一個濾波器就能恢復數字化且聚焦的超聲波向量。

使用 FIR 濾波器生成 ADC 輸出是一種簡單直觀的暴力方法,這里主要用于演示目的。在大多數設計中,ADC 輸出將使用傳統的積分器/低通濾波器解調器拓撲[2]生成。

參考資料

1. XPS 西格瑪-德爾塔(ΔΣ)型模數轉換器(ADC) V1.01A,DS587,2009 年 12 月 2 日

2. R. Steele, 增量調制系統, Pentech Press (倫敦), 1975 年

3. Digilent Cmod S6 參考手冊,Digilent Inc 公司, 2014 年 9 月 4 日

4. FT2232H 微型模塊產品說明書,V1.7,Future Technology Devices International Ltd.公司,2012 年

5. TFilter,免費在線 FIR 濾波器設計工具,http://t-filter.engineerjs.com/

6. USE 深度輔導,UG695 (V13.1),賽靈思公司,2011 年。

7. M.Bolatkale 和 L.J。Breems,高速和大帶寬西格瑪-德爾塔(ΔΣ)型 ADC

評論