fsp:fpga-pcb 文章 最新資訊

基于FPGA的卷積層并行加速方案

- 卷積神經(jīng)網(wǎng)絡(luò)(Convolutional?Neural?Networks)是一種主要應(yīng)用于圖像處理領(lǐng)域的人工智能算法。尤其是在計算機(jī)視覺領(lǐng)域,CNN在包括識別(recognition)、檢測(detection)、分割(segmentation)等很多任務(wù)中占主流地位。 卷積神經(jīng)網(wǎng)絡(luò)的基本元素:卷積層(convolutional?layer)、池化層(pooling)、激活函數(shù)(activation)、全連接層(fully-connected?layer)。卷

- 關(guān)鍵字: FPGA CNN

靜態(tài)哈夫曼編碼的快速硬件實現(xiàn)

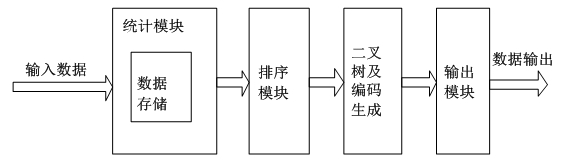

- 王朝馳?李成澤?史傲凱?李靖 電子科技大學(xué)(四川?成都?610054) 第一屆(2016-2017)全國大學(xué)生集成電路創(chuàng)新創(chuàng)業(yè)大賽全國總決賽FPGA設(shè)計方向二等獎本文所提出的方案的主要功能是連續(xù)接收256個0~9之間的任意數(shù)值,針對這256個數(shù)據(jù)完成輸入數(shù)據(jù)元素的哈夫曼編碼,最后先輸出0~9元素對應(yīng)的編碼,再按照輸入數(shù)據(jù)順序輸出各數(shù)據(jù)對應(yīng)的哈夫曼編碼。 1?系統(tǒng)設(shè)計方案 哈夫曼編碼的基本思想是將出現(xiàn)概率較大的數(shù)據(jù)用較短的編碼表示,而將出

- 關(guān)鍵字: 哈夫曼編碼 FPGA

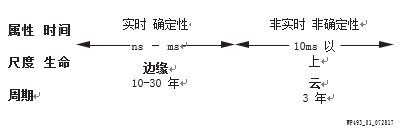

智能工業(yè)物聯(lián)網(wǎng)邊緣 (Edge)平臺的關(guān)鍵屬性(上)

- 1?IT-OT?融合方法 工業(yè)物聯(lián)網(wǎng)?(IIoT)?指涉及邊緣設(shè)備、云應(yīng)用、傳感器、算法、安全性、保密性、大量協(xié)議庫、人機(jī)界面?(HMI)?及其它必須互操作元素的多維度緊密耦合的系統(tǒng)鏈。一些人將?IIoT?愿景描述為運營技術(shù)?(OT)?與信息技術(shù)?(IT)?的融合,但實際上目標(biāo)更為深遠(yuǎn)。OT?應(yīng)用的時間敏感性和?IT?應(yīng)用的數(shù)據(jù)密集性要求所有這些元素融

- 關(guān)鍵字: 工業(yè)物聯(lián)網(wǎng) FPGA

采用FPGA的以太網(wǎng)應(yīng)用

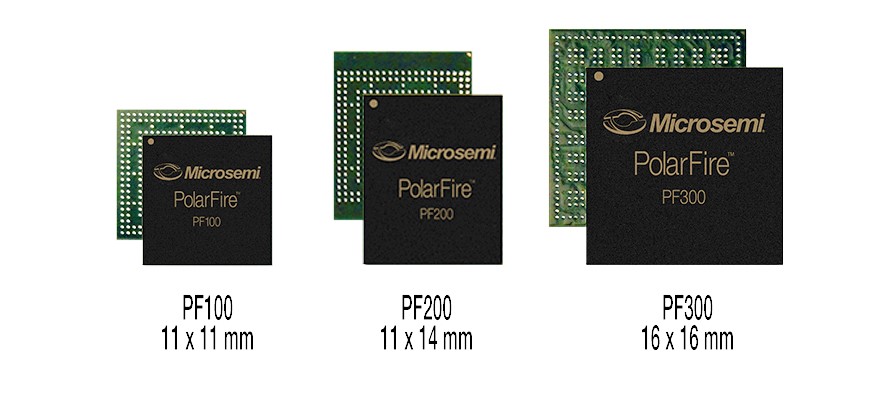

- 以太網(wǎng)連接的日益普及和不斷增加的降成本壓力,是不可阻擋的兩大網(wǎng)絡(luò)趨勢。由于網(wǎng)絡(luò)和物聯(lián)網(wǎng)(IoT)不斷擴(kuò)張,使得以太網(wǎng)端口的性能持續(xù)增加,并且應(yīng)用于更廣泛的各種產(chǎn)品。網(wǎng)絡(luò)運營商面臨兩個巨大壓力,首先是要大幅降低資本支出(CAPEX/OPEX),同時要提供更快性能以支持消費者應(yīng)用,如4?K視頻和無處不在的云連接。為了幫助架構(gòu)師滿足這些市場需求,我們需要重新定義中端密度FPGA特性:低成本、低功耗,并且可以滿足通訊應(yīng)用中以太網(wǎng)互聯(lián)的性能要求。 這些新市場向設(shè)計以太網(wǎng)通信設(shè)備的供應(yīng)商提出了重大的挑

- 關(guān)鍵字: FPGA 以太網(wǎng)

AI技術(shù)助力視頻監(jiān)控領(lǐng)域智能化發(fā)展

- 如果大家參加過2017年10月底在深圳舉辦的安博會,肯定會被如潮的人海以及玲瑯滿目的人工智能案例所震驚。毫無疑問,視頻監(jiān)控行業(yè)將迎來真正的大爆發(fā),同時人工智能也必然會在視頻監(jiān)控行業(yè)大規(guī)模應(yīng)用。 近兩年,得益于深度學(xué)習(xí)算法的進(jìn)步,人工智能得以飛速發(fā)展和應(yīng)用。業(yè)界有個這樣的簡單比喻:如果把打造人工智能系統(tǒng)比作造火箭,則算法是引擎,數(shù)據(jù)是燃料,加速靠的是芯片。可見,海量的數(shù)據(jù)、先進(jìn)的算法、高效的芯片是AI領(lǐng)域三大要素。在這次人工智能大浪潮中,幾乎每個芯片商都希望搭上順風(fēng)車火一把。下圖為研究機(jī)構(gòu)對未來AI芯

- 關(guān)鍵字: AI FPGA

大咖詳談FPGA,簡介、工作原理等

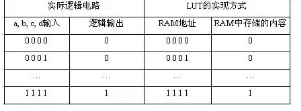

- FPGA工作原理與簡介 如前所述,F(xiàn)PGA是在PAL、GAL、EPLD、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為ASIC領(lǐng)域中的一種半定制電路而出現(xiàn)的,即解決了定制電路的不足,又克服了原有可編程器件門電路有限的缺點。 由于FPGA需要被反復(fù)燒寫,它實現(xiàn)組合邏輯的基本結(jié)構(gòu)不可能像ASIC那樣通過固定的與非門來完成,而只能采用一種易于反復(fù)配置的結(jié)構(gòu)。查找表可以很好地滿足這一要求,目前主流FPGA都采用了基于SRAM工藝的查找表結(jié)構(gòu),也有一些軍品和宇航級FPGA采用Flash或者熔絲與反熔

- 關(guān)鍵字: FPGA Xilinx

說說那些你不知道的電路設(shè)計及PCB布線時的可靠性原則

- 目前電子器材用于各類電子設(shè)備和系統(tǒng)仍然以印制電路板為主要裝配方式。實踐證明,即使電路原理圖設(shè)計正確,印制電路板設(shè)計不當(dāng),也會對電子設(shè)備的可靠性產(chǎn)生不利影響。 因此,在設(shè)計印制電路板的時候,應(yīng)注意采用正確的方法。 一、接地 地線設(shè)計在電子設(shè)備中,接地是控制干擾的重要方法。如能將接地和屏蔽正確結(jié)合起來使用,可解決大部分干擾問題。電子設(shè)備中地線結(jié)構(gòu)大致有系統(tǒng)地、機(jī)殼地(屏蔽地)、數(shù)字地(邏輯地)和模擬地等。 在地線設(shè)計中應(yīng)注意以下幾點 正確選擇單點接地與多點接地在低頻電路中,信號的工作頻率小于1M

- 關(guān)鍵字: PCB 電路設(shè)計

PCB設(shè)計中,布局布線有哪些基本原則

- 一、元件布局基本規(guī)則 1. 按電路模塊進(jìn)行布局,實現(xiàn)同一功能的相關(guān)電路稱為一個模塊,電路模塊中的元件應(yīng)采用就近集中原則,同時數(shù)字電路和模擬電路分開; 2.定位孔、標(biāo)準(zhǔn)孔等非安裝孔周圍1.27mm 內(nèi)不得貼裝元、器件,螺釘?shù)劝惭b孔周圍3.5mm(對于M2.5)、4mm(對于M3)內(nèi)不得貼裝元器件; 3. 臥裝電阻、電感(插件)、電解電容等元件的下方避免布過孔,以免波峰焊后過孔與元件殼體短路; 4. 元器件的外側(cè)距板邊的距離為5mm; 5. 貼裝

- 關(guān)鍵字: PCB 布線

據(jù)說電子工程師就易犯這20個錯,你有過嗎?

- 電子工程師指從事各類電子設(shè)備和信息系統(tǒng)研究、教學(xué)、產(chǎn)品設(shè)計、科技開發(fā)、生產(chǎn)和管理等工作的高級工程技術(shù)人才。一般分為硬件工程師和軟件工程師。 硬件工程師:主要負(fù)責(zé)電路分析、設(shè)計;并以電腦軟件為工具進(jìn)行PCB設(shè)計,待工廠PCB制作完畢并且焊接好電子元件之后進(jìn)行測試、調(diào)試; 軟件工程師:主要負(fù)責(zé)單片機(jī)、DSP、ARM、FPGA等嵌入式程序的編寫及調(diào)試。FPGA程序有時屬硬件工程師工作范疇。 錯誤一: 這些拉高/拉低的電阻用多大的阻值關(guān)系不大,就選個整數(shù)5K吧 點評:市場上不存在5K的阻值,最接近的

- 關(guān)鍵字: PCB FPGA

為什么說在嵌入式系統(tǒng)設(shè)計采用FPGA是理想的選擇?

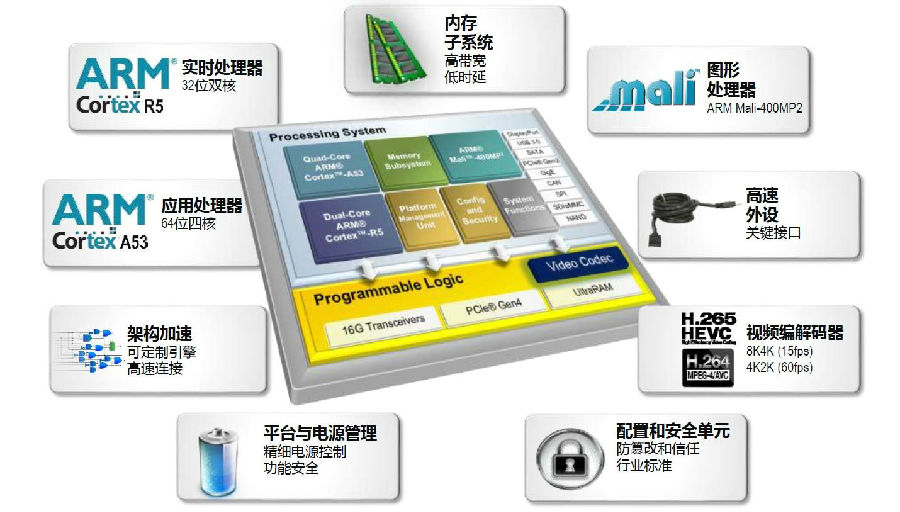

- 隨著消費電子、物聯(lián)網(wǎng)等領(lǐng)域的不斷發(fā)展,用戶需求也越來越復(fù)雜和多樣,因此我們在嵌入式系統(tǒng)設(shè)計中必須選擇合適的處理器(SoC)系統(tǒng),當(dāng)然我們也需要考慮成本、功耗、性能、I/O資源等方面,但是隨著實踐案例的增多FPGA越來越成為嵌入式系統(tǒng)設(shè)計的主流選擇。 Xilinx作為可編程邏輯器件(FPGA)的行業(yè)領(lǐng)導(dǎo)者提供了豐富的器件和簡捷的開發(fā)工具,下面從以下幾方面向大家介紹: FPGA/SoC:最早我們都采用的是純FPGA設(shè)計,利用FPGA的資源實現(xiàn)軟核處理器比如Microblaze、Picoblaze等,現(xiàn)

- 關(guān)鍵字: FPGA 嵌入式

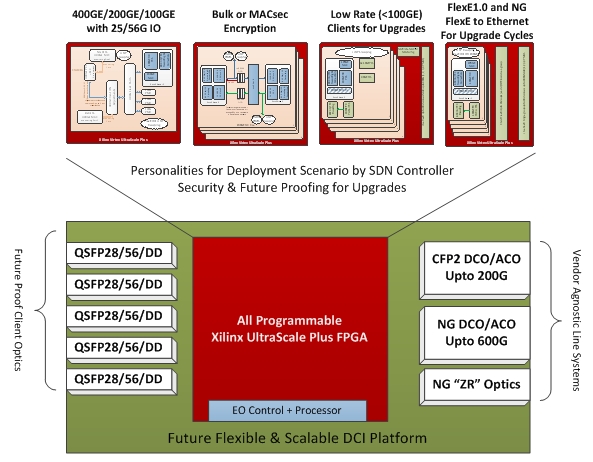

可編程邏輯實現(xiàn)數(shù)據(jù)中心互連

- 隨著實施基于云的服務(wù)和機(jī)器到機(jī)器通信所產(chǎn)生的數(shù)據(jù)呈指數(shù)級增長,數(shù)據(jù)中心面臨重重挑戰(zhàn)。 這種增長毫無減緩態(tài)勢,有業(yè)界專家預(yù)測內(nèi)部數(shù)據(jù)中心機(jī)器對機(jī)器流量將會超出所有其他類型流量多個數(shù)量級。這種顯著增長給數(shù)據(jù)中心帶來三個主要挑戰(zhàn): ·?數(shù)據(jù)速度?–?接收與處理數(shù)據(jù)所需的時間增強(qiáng)了數(shù)據(jù)的接收和處理能力,實現(xiàn)高速傳輸。這使數(shù)據(jù)中心可支持近乎實時的性能。 ·?數(shù)據(jù)種類?–?從圖像與視頻這樣的結(jié)構(gòu)化數(shù)據(jù)到傳感器與日志數(shù)據(jù)這樣的非結(jié)構(gòu)化數(shù)據(jù),可將不同格

- 關(guān)鍵字: DCI FPGA

美高森美宣布其整個產(chǎn)品組合不受Spectre和Meltdown漏洞影響

- 致力于在功耗、安全、可靠性和性能方面提供差異化半導(dǎo)體技術(shù)方案的領(lǐng)先供應(yīng)商美高森美公司(Microsemi Corporation,紐約納斯達(dá)克交易所代號:MSCC)宣布旗下包括現(xiàn)場可編程邏輯器件(FPGA)在內(nèi)的產(chǎn)品均不受最近發(fā)現(xiàn)的x86、ARM?及其它處理器相關(guān)的安全漏洞所影響。早前安全研究人員透露全球范圍內(nèi)涉及數(shù)十億臺設(shè)備的芯片存在稱為Spectre 和 Meltdown 的主要計算機(jī)芯片漏洞。 美高森美首席技術(shù)官兼高級開發(fā)副總裁Jim Aral

- 關(guān)鍵字: 美高森美 FPGA

“和諧”升級“復(fù)興”萬億級市場,且看他們?nèi)绾梧⒌妙^湯

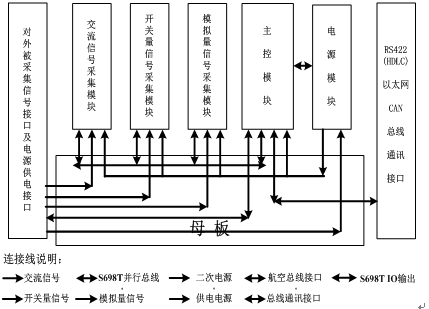

- 2017年6月26日,中國新一代高鐵“復(fù)興號”實現(xiàn)了上海與北京之間雙向首發(fā),最高上檔時速400公里,標(biāo)準(zhǔn)時速達(dá)到350公里,跑完京滬全程僅需3小時!中國高鐵開始由“和諧”時代進(jìn)化到“復(fù)興”時代。 疾馳的列車不止是速度與激情的體驗,更是中國鐵路技術(shù)的一大躍進(jìn),以及巨大的軌道交通市場升級:據(jù)預(yù)計到2030年,全球鐵路規(guī)劃新建里程將達(dá)10萬公里(不含中國),其中高鐵4萬公里以上,直接投資1.1萬億美元;機(jī)械和電氣的統(tǒng)一互聯(lián)互通、規(guī)范化操作、以及包括牽引、高壓、轉(zhuǎn)

- 關(guān)鍵字: 電子展 PCB

fsp:fpga-pcb介紹

您好,目前還沒有人創(chuàng)建詞條fsp:fpga-pcb!

歡迎您創(chuàng)建該詞條,闡述對fsp:fpga-pcb的理解,并與今后在此搜索fsp:fpga-pcb的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對fsp:fpga-pcb的理解,并與今后在此搜索fsp:fpga-pcb的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司