fsp:fpga-pcb 文章 最新資訊

六大技巧教你如何傳遞PCB原理圖到版圖設計

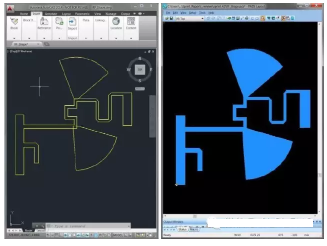

- 將PCB原理圖傳遞給版圖(layout)設計時需要考慮的六件事。提到的所有例子都是用Multisim設計環(huán)境開發(fā)的,不過在使用不同的EDA工具時相同的概念同樣適用哦! 初始原理圖傳遞 通過網(wǎng)表文件將原理圖傳遞到版圖環(huán)境的過程中還會傳遞器件信息、網(wǎng)表、版圖信息和初始的走線寬度設置。 下面是為版圖設計階段準備的一些推薦步驟: 1.將柵格和單位設置為合適的值。為了對元器件和走線實現(xiàn)更加精細的布局控制,可以將器件柵格、敷銅柵格、過孔柵格和SMD柵格設計為1mil. 2.將電路板外框空白區(qū)和過孔設成要

- 關鍵字: PCB

不同制造工藝對PCB上的焊盤會有啥影響和要求?

- 1、貼片元器件兩端沒連接插裝元器件的必須增加測試點,測試點直徑在1.0mm~1.5mm之間為宜,以便于在線測試儀測試。測試點焊盤的邊緣至少離周圍焊盤邊緣距離0.4mm。測試焊盤的直徑在1mm以上,且必須有網(wǎng)絡屬性,兩個測試焊盤之間的中心距離應大于或等于2.54mm;若用過孔做為測量點,過孔外必須加焊盤,直徑在1mm(含)以上; 2、有電氣連接的孔所在的位置必須加焊盤;所有的焊盤,必須有網(wǎng)絡屬性,沒有連接元件的網(wǎng)絡,網(wǎng)絡名不能相同;定位孔中心離測試焊盤中心的距離在3mm以上;其他不規(guī)則形狀,但有電氣連

- 關鍵字: PCB

為什么設計射頻、微波PCB難度如此之大?這些技巧你該掌握

- 簡介 如今的電子產(chǎn)品已經(jīng)不再像上世紀 70 年代的電視和電冰箱一樣,消費者每隔十年才更新?lián)Q代一次。現(xiàn)在幾乎每個家庭的每位成員都是電子產(chǎn)品的消費者,而且隨著科技發(fā)展不斷為智慧手機、平板計算機、汽車和電視帶來各種人們消費得起的新功能,人們每年都會購買新產(chǎn)品。 這些電子產(chǎn)品的共同特征之一是采用無線技術,而該技術極度依賴于RF射頻電路。遺憾的是,即使是最自信的設計人員,對于射頻電路也往往望而卻步,因為它會帶來巨大的設計挑戰(zhàn),并且需要專業(yè)的設計和分析工具。正因為如此,許多年來,PCB的射

- 關鍵字: 射頻 PCB

聽老工程師講解PCB布局經(jīng)驗

- 對于電子產(chǎn)品來說,印制線路板設計是其從電原理圖變成一個具體產(chǎn)品必經(jīng)的一道設計工序,其設計的合理性與產(chǎn)品生產(chǎn)及產(chǎn)品質量緊密相關,而對于許多剛從事電子設計的人員來說,在這方面經(jīng)驗較少,雖然已學會了印制線路板設計軟件,但設計出的印制線路板常有這樣那樣的問題,而許多電子刊物上少有這方面文章介紹,筆者曾多年從事印制線路板設計的工作,在此將印制線路板設計的點滴經(jīng)驗與大家分享,希望能起到拋磚引玉的作用。筆者的印制線路板設計軟件早幾年是TANGO,現(xiàn)在則使用PROTEL2.7 FOR WINDOWS。 板的布局

- 關鍵字: PCB

比較PCB的接地三種方式的區(qū)別

- 接地為防止觸電或保護設備的安全,把電力電訊等設備的金屬底盤或外殼接上地線;利用大地作電流回路接地線。在電力系統(tǒng)中,將設備和用電裝置的中性點、外 殼或支架與接地裝置用導體作良好的電氣連接叫做接地。接地的功用除了將一些無用的電流或是噪聲干擾導入大地外,最大功用為保護使用者不被電擊,以 UPS 而言,有些 UPS 會將零線與地線間的電壓標示出來,確保產(chǎn)品不會造成對人體的電擊傷害。 1.單點接地 工作頻率低(<1MHz)的采用單點接地式(即把整個電路系 統(tǒng)中的一個結構點看作接地參考點,所有對

- 關鍵字: PCB

fsp:fpga-pcb介紹

您好,目前還沒有人創(chuàng)建詞條fsp:fpga-pcb!

歡迎您創(chuàng)建該詞條,闡述對fsp:fpga-pcb的理解,并與今后在此搜索fsp:fpga-pcb的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對fsp:fpga-pcb的理解,并與今后在此搜索fsp:fpga-pcb的朋友們分享。 創(chuàng)建詞條

關于我們 -

廣告服務 -

企業(yè)會員服務 -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司