fpga-spartan 文章 最新資訊

SignalTapII ELA的FPGA在線調試技術

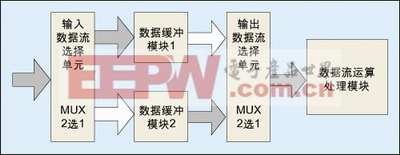

- 通過對FPGA內部信號的捕獲測試,可以實現(xiàn)對系統(tǒng)設計缺陷的實時分析和修正。與外部測試設備相比,可以總結出SignalTapII ELA的幾點優(yōu)越性:不占用額外的I/O引腳,不占用PCB上的空間,不破壞信號的時序和完整性,不需額外費用;從多方面證實,該測試手段可以減少調試時間,縮短設計周期。

- 關鍵字: SignalTapII FPGA ELA 在線調試

AEMB軟核處理器的SoC系統(tǒng)驗證平臺的構建

- SoC芯片的規(guī)模一般遠大于普通的ASIC,同時深亞微米工藝帶來的設計困難等使得SoC設計的復雜度大大提高。仿...

- 關鍵字: FPGA SoC 系統(tǒng)驗證平臺 AEMB 軟核處理器

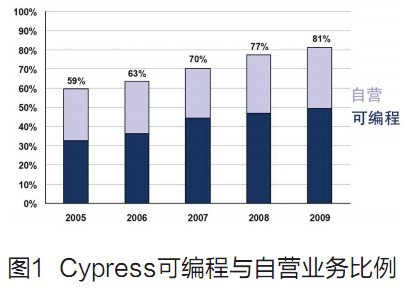

可編程和自營業(yè)務是提升利潤的竅門

- 在芯片市場,很多廠商在追逐著摩爾定律,例如CPU、存儲器、FPGA等產品靠工藝的進步來降低單位成本,靠大批量通用產品來獲利。除此之外,另一種可取的方法是做高附加價值產品。不久前,Cypress公司市場傳訊部高級總監(jiān)Joseph L. McCarthy向本刊介紹了該公司這幾年的戰(zhàn)略轉型:該公司正從做通用產品轉為可編程器件和自營產品上來(圖1),2009年可編程和自營產品比例已達到81%。這兩部分可使產品的單價上升,產生更高的利潤。 PSoC/觸控可編程戰(zhàn)略 為了實施可編程戰(zhàn)略,2003年

- 關鍵字: Cypress 摩爾定律 CPU 存儲器 FPGA 201005

fpga-spartan介紹

您好,目前還沒有人創(chuàng)建詞條fpga-spartan!

歡迎您創(chuàng)建該詞條,闡述對fpga-spartan的理解,并與今后在此搜索fpga-spartan的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對fpga-spartan的理解,并與今后在此搜索fpga-spartan的朋友們分享。 創(chuàng)建詞條

熱門主題

關于我們 -

廣告服務 -

企業(yè)會員服務 -

網站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司