EEPW首頁(yè) >>

主題列表 >>

fpga-nios

fpga-nios 文章 最新資訊

深層解析FPGA

- 概覽高端設(shè)計(jì)工具很少有甚至是沒有硬件設(shè)計(jì)技術(shù)的工程師和科學(xué)家提供現(xiàn)場(chǎng)可編程門陣列(FPGA)。無論你使用圖形化設(shè)計(jì)程序,ANSI C語言還是VHDL語言,如此復(fù)雜的合成工藝會(huì)不禁讓人去想FPGA真實(shí)的運(yùn)作情況。在這個(gè)芯

- 關(guān)鍵字: FPGA

FPGA構(gòu)成3/3相雙繞組感應(yīng)發(fā)電機(jī)勵(lì)磁控制系統(tǒng)

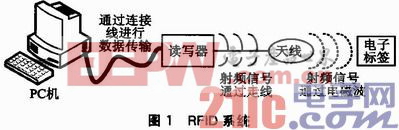

- FPGA構(gòu)成3/3相雙繞組感應(yīng)發(fā)電機(jī)勵(lì)磁控制系統(tǒng) 1系統(tǒng)簡(jiǎn)介3/3相雙繞組感應(yīng)發(fā)電機(jī)帶有兩個(gè)繞組:勵(lì)磁補(bǔ)償繞組和功率繞組,如圖1所示。勵(lì)磁補(bǔ)償繞組上接一個(gè)電力電子變換裝置,用來提供感應(yīng)發(fā)電機(jī)需要的無功功率,使功率繞

- 關(guān)鍵字: FPGA 雙繞組 感應(yīng)發(fā)電機(jī) 勵(lì)磁控制

免費(fèi)的 I/O:改進(jìn) FPGA 時(shí)鐘分配控制(圖)

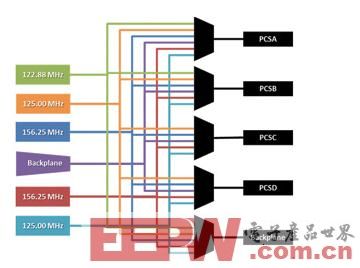

- 同步數(shù)字系統(tǒng)中的時(shí)鐘信號(hào)(如遠(yuǎn)程通信中使用的)為系統(tǒng)中的數(shù)據(jù)傳送定義了時(shí)間基準(zhǔn)。一個(gè)時(shí)鐘分配網(wǎng)絡(luò)由多個(gè)時(shí)鐘信號(hào)組成,由一個(gè)點(diǎn)將所有信號(hào)分配給需要時(shí)鐘信號(hào)的所有組件。因?yàn)闀r(shí)鐘信號(hào)執(zhí)行關(guān)鍵的系統(tǒng)功能,很顯然應(yīng)給予更多的關(guān)注,不僅在時(shí)鐘的特性(即偏移和抖動(dòng))方面,還有那些組成時(shí)鐘分配網(wǎng)絡(luò)的組件。 FPGA開發(fā)團(tuán)隊(duì)不斷面臨過于繁瑣、復(fù)雜的時(shí)鐘網(wǎng)絡(luò)的挑戰(zhàn)。各種因素,包括不斷增加的I/O需求、降低成本的要求和減少印刷電路板設(shè)計(jì)更改的需要,迫使設(shè)計(jì)人員重新審視時(shí)鐘網(wǎng)絡(luò)。本文將探討FPGA時(shí)鐘分配控制方面的挑戰(zhàn)

- 關(guān)鍵字: FPGA 時(shí)鐘

fpga-nios介紹

您好,目前還沒有人創(chuàng)建詞條fpga-nios!

歡迎您創(chuàng)建該詞條,闡述對(duì)fpga-nios的理解,并與今后在此搜索fpga-nios的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)fpga-nios的理解,并與今后在此搜索fpga-nios的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司