FPGA中可配置邏輯塊(CLB)

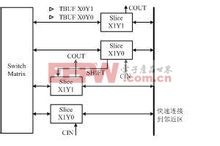

CLB是FPGA內的基本邏輯單元。CLB的實際數量和特性會依器件的不同而不同,但是每個CLB都包含一個可配置開關矩陣,此矩陣由4或6個輸入、一些 選型電路(多路復用器等)和觸發器組成。開關矩陣是高度靈活的,可以對其進行配置以便處理組合邏輯、移位寄存器或RAM。在Xilinx公司的FPGA器件中,CLB由多個(一般為4個或2個)相同的Slice和附加邏輯構成,如圖1-3所示。每個CLB模塊不僅可以用于實現組合邏輯、時序邏輯,還可以配置為分布式RAM和分布式ROM。

本文引用地址:http://www.104case.com/article/189768.htm

典型的CLB結構示意圖

典型的CLB結構示意圖Slice是Xilinx公司定義的基本邏輯單位,其內部結構如圖1-4所示,一個Slice由兩個4輸入的函數、進位邏輯、算術邏輯、存儲邏輯和函數復用器組成。算術邏輯包括一個異或門(XORG)和一個專用與門(MULTAND),一個異或門可以使一個Slice實現 2bit全加操作,專用與門用于提高乘法器的效率;進位邏輯由專用進位信號和函數復用器(MUXC)組成,用于實現快速的算術加減法操作;4輸入函數發生 器用于實現4輸入LUT、分布式RAM或16比特移位寄存器(Virtex-5系列芯片的Slice中的兩個輸入函數為6輸入,可以實現6輸入LUT或 64比特移位寄存器);進位邏輯包括兩條快速進位鏈,用于提高CLB模塊的處理速度。

評論