- 現場可編程邏輯閘陣列芯片(FPGA)近年來加速取代特殊應用芯片(ASIC)市場,FPGA雙雄賽靈思(Xilinx)與阿爾特拉(Altera)先后推出28納米FPGA產品,可望加速FPGA取代ASIC市場,賽靈思亞太區營銷及應用總監張宇清指出,28納米FPGA可大幅提升效能,并降低功耗與價格,拓展以往FPGA無法取代的ASIC市場,加速FPGA 市場的成長力道。

張宇清指出,FPGA要取代ASIC市場有4大障礙,包括需要提高更大的容量、更高的系統效能、更低的功耗與更低的成本,過去在40納米雖然已有

- 關鍵字:

FPGA ASIC 28納米

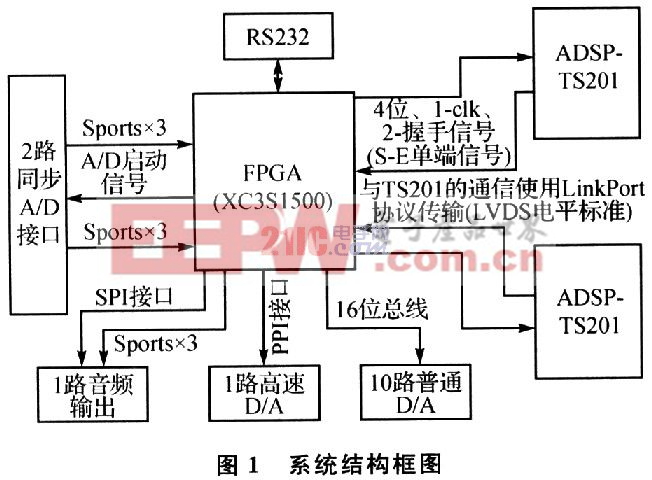

- FPGA與DSP信號處理系統的散熱設計,引言

隨著系統性能的不斷提升,系統功耗也隨之增大,如何對系統進行有效的散熱,控制系統溫度滿足芯片的正常工作條件變成了一個十分棘手的問題。通常使用風冷技術對系統進行散熱。采用風冷技術時要重點考慮散熱

- 關鍵字:

散熱 設計 理系 處理 DSP 信號 FPGA

- 摘要:突發模式誤碼測試儀與一般連續誤碼測試儀不同,其接收端在誤碼比對前要實現在十幾位內,對具有相位跳變特點的信號進行時鐘提取和數據恢復,并且在誤碼比對時須濾除前導碼和定界符,僅對有效數據進行誤碼統計。

- 關鍵字:

FPGA 模式 誤碼測試儀 實現方案

- 介紹了應用現場可編程門陣列(FPGA)設計和實現通用異步收發器UART的方法。采用有限狀態機模型形式化描述了UART的功能,在此基礎上用硬件描述語言VHDL編程實現了UART,并使用QuartusⅡ軟件中的嵌入式邏輯分析儀SignalTapⅡ對數據傳輸進行了檢測,驗證了設計的正確性。

- 關鍵字:

FPGA UART

- 摘要:為提高8B/10B編解碼的工作速度和簡化邏輯方法,提出一種基于FPGA的8B/10B編解碼系統設計方案。與現有的8B/10B編解碼方案相比,該方案是一種利用FPGA實現8B/lOB編解碼的模塊方法,接收模塊在收到外部發送的

- 關鍵字:

FPGA 10B 編解碼

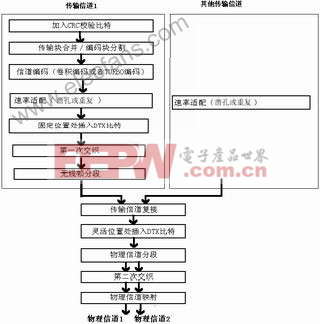

- 基于WCDMA速率適配算法的FPGA設計,隨著因特網爆炸性的增長以及各種無線業務需求的增加,傳統的無線通信網已經越來越無法適應人們的需要。因此,以大容量、高數據率和承載多媒體業務為目的的第三代移動通信系統(IMT-2000)應運而生。碼分多址(CDMA)由于

- 關鍵字:

FPGA 設計 算法 適配 WCDMA 速率 基于

- Altera公司今天發布Stratix® V系列FPGA,適用于支持Micron技術公司的下一代低延時DRAM (RLDRAM® 3存儲器)。Stratix V FPGA采用新的存儲器體系結構,降低延時,高效實現FPGA業界最好的系統性能。Stratix V FPGA為網絡設備生產商提供存儲器接口解決方案,支持在互聯網上迅速有效的傳送視頻、語音和數據。

Micron公司業務開發高級經理Bruce Franklin表示:“Micron的下一代RLDRAM 3存儲器專門設

- 關鍵字:

Altera Stratix FPGA

- 摘要:提出了一種IRIG-B(DC)碼產生電路的設計方法。采用Altera公司低功耗Cyclone FPGA系列中的EPlC6T144、8段數碼管、晶體振蕩器和MAX3232E等器件構成硬件電路、使用VHDL語言設計IRIG-B直流時間碼的軟件。為了設置和

- 關鍵字:

IRIG-B FPGA DC 產生電路

- 摘要:提出一種基于FPGA的PCI硬件加解密卡的設計方案,用硬件加解密取代了傳統的軟件加解密,將加解密模塊和PCI接口模塊集成在一個FPGA芯片內實現。分析了PCI加解密卡的軟硬件的結構和原理,詳細介紹了DESX加解密算法

- 關鍵字:

FPGA PCI 硬件 加解密

- 根據CMI碼的特性,介紹了一種新的編程思路實現CMI編碼,在Max+PlusⅡ開發平臺上使用VHDL編程實現CMI編碼,并得到仿真波形。實驗結果表明,這種編程思路簡單、清晰。在產生7位偽隨機序列的前提下,分別對“O”,“1”進行編碼。這種思路為其他碼型設計提供了參考。

- 關鍵字:

CPLD FPGA CMI 編碼

- 在高速移動下,OFDM系統載波間正交性被破壞,出現載波間干擾(ICI),嚴重影響系統性能,必須采用適當的均衡技術以補償ICI。為了保證通信的有效性和實時性要求,使用FPGA實現了一種低復雜度的最小均方誤差(MMSE)OFDM均衡器算法。在ISE軟件平臺上使用Verilog語言編寫程序,并在Xilinx公司Virtex-2實驗板(XC2V930芯片)上對設計進行了驗證。

- 關鍵字:

OFDM FPGA 移動 均衡器

- 摘要:基于FPGA的應用技術,采用Altera公司DE2-70開發板的CycloneⅡ系列EP2C70作為核心器件,設計了一種基于FPGA的新型可調信號發生器。通過QuartusⅡ軟件及Vetilog HDL編程語言設計LPM_ROM模塊定制數據ROM,并通過地

- 關鍵字:

FPGA 信號發生器

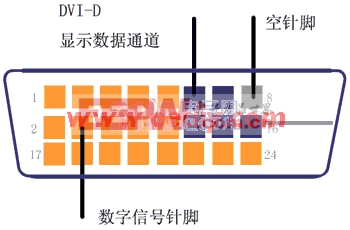

- 隨著數字技術的飛速發展,各種數字顯示屏也隨即涌現出來有led、LCD、DLP等,各種數字大屏幕的控制系統多種多樣,有用ARM+FPGA脫機控制系統,也有用PC+DVI接口解碼芯片+FPGA芯片聯機控制系統,在這里我們講述一種不僅

- 關鍵字:

圖像 顯示系統 系統 設計 大屏幕 LED FPGA 芯片 控制

fpga-ask介紹

您好,目前還沒有人創建詞條fpga-ask!

歡迎您創建該詞條,闡述對fpga-ask的理解,并與今后在此搜索fpga-ask的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473