基于FPGA的可調信號發生器

摘要:基于FPGA的應用技術,采用Altera公司DE2-70開發板的CycloneⅡ系列EP2C70作為核心器件,設計了一種基于FPGA的新型可調信號發生器。通過QuartusⅡ軟件及Vetilog HDL編程語言設計LPM_ROM模塊定制數據ROM,并通過地址指針讀取ROM中不同區域的數據,根據讀取數據間隔的不同,實現調整頻率功能,該系統可產生正弦波、方波、三角波和鋸齒波4種波形信號,并使用嵌入式邏輯分析儀對產生的不同波形信號進行實時測試,實驗證明,該可調信號發生器系統軟件模擬數據和理論定制波形相吻合。

關鍵詞:信號發生器;EP2C70;Vetjlog HDL;FPGA

傳統信號發生器大多由模擬電路構成,存在連線復雜、調試煩瑣且可靠性較差等缺點。以Verilog HDL編程語言和FPGA器件為核心的可調信號發生器的設計實現,提高了系統可靠性,實現了系統信號實時快速測量,也為其廣泛應用于實際領域創造了條件。

1 系統總體設計

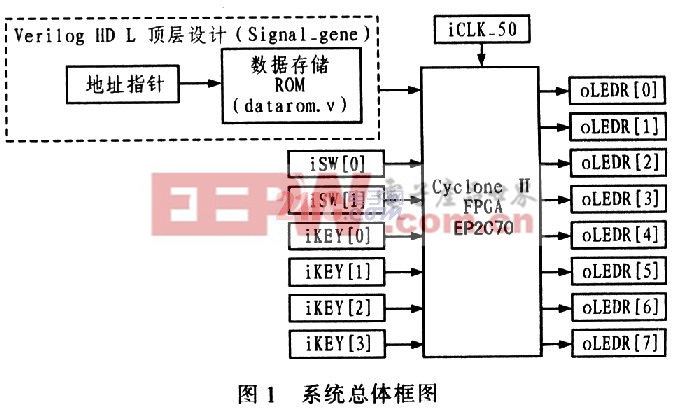

可調信號發生器系統由頂層模塊、EP2C70器件、控制開關和輸入輸出模塊等部分組成,如圖l所示。在FPGA中實現的頂層文件包含地址指針和數據ROM2部分。其中,數據ROM由QuartusⅡ軟件中的LPM_ROM模塊構成,能達到最優設計,LPM_ROM由FPGA中的EAB或ESB實現。數據ROM中存儲正弦波、方波、三角波和鋸齒波4種信號各1個周期的波形數據(在此選擇1個周期128個數據樣點),地址指針讀取ROM中不同區域的數據,可產生不同的波形,并通過使用嵌入式邏輯分析儀SignalTapⅡ進行實時測試。根據讀取數據間隔的不同,即可實現調整頻率的功能。

2 系統功能模塊設計

可調信號發生器系統的功能模塊主要由頂層文件(Verilog HDL源程序)和波形數據ROM兩部分組成。波形數據ROM設計主要包括設計波形數據ROM初始化數據文件和定制ROM元件(datarom.v)。

2.1 頂層文件設計

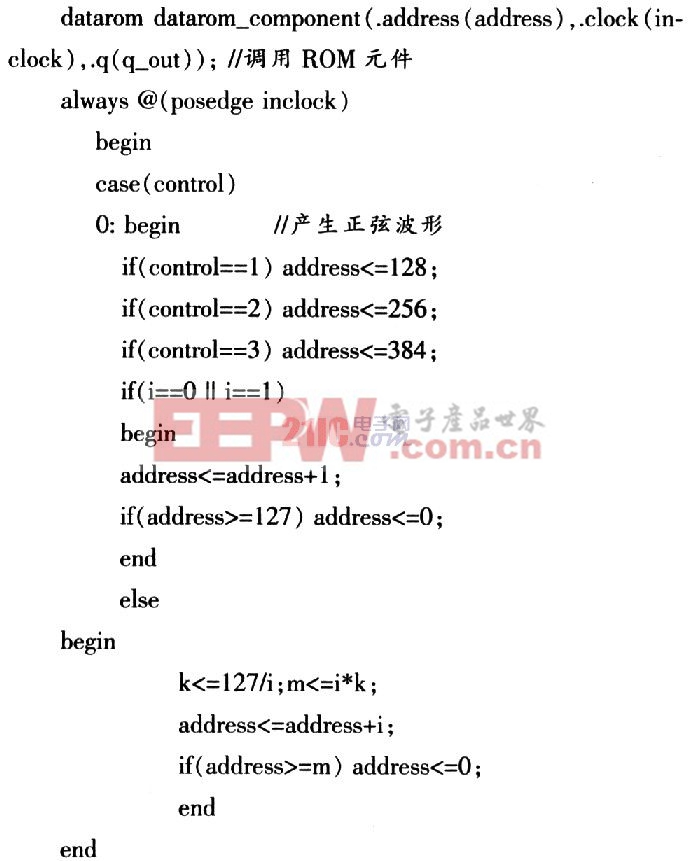

本系統采用Ahera公司的CycloneⅡ系列EP2C70器件作為核心,通過QuartusⅡ軟件編寫Verilog HDL源程序,實現一個可以產生正弦波、方波、三角波和鋸齒波4種波形信號,并且能夠實現信號轉換及頻率可調功能的信號發生器。其中control控制產生波形的種類,00、0l、10、11分別產生正弦波、方波、三角波和鋸齒波;i控制讀取數據間隔,調整頻率。產生正弦波的源程序如下:

評論