fpga+dsp 文章 最新資訊

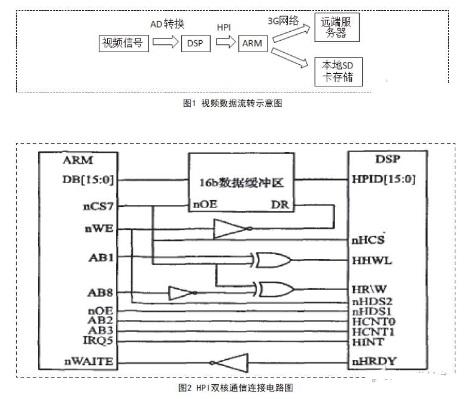

基于ARM11和DSP協(xié)作視頻流處理技術(shù)的3G視頻安全帽設(shè)計

- 1.引言 為提高在高危工作場所現(xiàn)場作業(yè)的可控性,本文采用仿生學(xué)原理和高集成度設(shè)計實現(xiàn)了與人眼同視角的3G視頻安全帽。本設(shè)計由視頻安全帽和腰跨式數(shù)據(jù)處理終端兩部分組成,采用高可靠性航空插頭連接。其中圖像處理采用三星公司的S3C6410ARM11處理器和TMS320DM642 DSP處理器組成。本設(shè)計結(jié)合DSP處理器在視頻壓縮方面的優(yōu)勢和運行于ARM之上的Linux操作系統(tǒng)在數(shù)據(jù)管理與任務(wù)調(diào)度機制方面的出色表現(xiàn),由DSP完成圖像處理功能,并通過高速接口把視頻數(shù)據(jù)傳輸給嵌入式微處理系統(tǒng),完成視頻數(shù)據(jù)的

- 關(guān)鍵字: ARM11 DSP

一種基于FPGA的OLED顯示系統(tǒng)

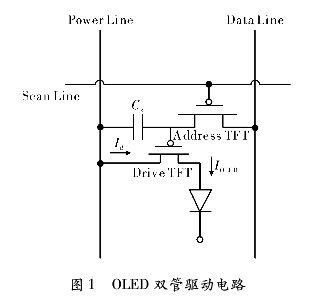

- 針對LCD顯示屏溫度適應(yīng)性差、可視角度小、LCD的通用驅(qū)動電路實現(xiàn)的對比度較低等缺點,采用OLED作為顯示器件,設(shè)計并實現(xiàn)了一種使用FPGA驅(qū)動OLED的顯示系統(tǒng)。采用PIC16F690單片機作為微處理器控制整機時序,利用FPGA進行視頻信號處理,完成格式轉(zhuǎn)換、色空間處理以及隔行轉(zhuǎn)逐行操作,最終實現(xiàn)驅(qū)動顯示。系統(tǒng)的測試結(jié)果表明,該方案不僅能顯著提高畫面對比度,而且能穩(wěn)定顯示監(jiān)控圖像,為后繼功能的拓展提供了平臺。 一種基于FPGA的OLED顯示系統(tǒng).pdf

- 關(guān)鍵字: FPGA OLED

基于FPGA的OLED真彩色動態(tài)圖像顯示的實現(xiàn)

- 作為第3代顯示器,有機電致發(fā)光器件(Organic Light Emitting Diode,OLED)由于其主動發(fā)光、響應(yīng)快、高亮度、全視角、直流低壓驅(qū)動、全固態(tài)以及不易受環(huán)境影響等優(yōu)異特性,具有LCD無法比擬的優(yōu)點,在手機、個人電子助理(PDA)、數(shù)碼相機、車載顯示、筆記本電腦、壁掛電視以及軍事領(lǐng)域都具有廣闊的應(yīng)用前景,因而得到了業(yè)界廣泛的關(guān)注。OLED發(fā)展至今,已經(jīng)由最初的單色發(fā)展到現(xiàn)在的全彩,與此同時對驅(qū)動電路也提出了更高的要求,由最初的無灰階單色靜態(tài)驅(qū)動,到彩色動態(tài)驅(qū)動。 目前,OLE

- 關(guān)鍵字: FPGA OLED

FPGA是什么

- FPGA是英文Field Programmable Gate Array的縮寫,即現(xiàn)場可編程門陣列,它是在PAL、GAL、EPLD等可編程器件的基礎(chǔ)上進一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點。 FPGA——工作原理 FPGA采用了邏輯單元陣列LCA(Logic Cell Array)這樣一個概念,內(nèi)部包括可配置邏輯模塊CLB(Configurable Logic

- 關(guān)鍵字: FPGA Xilinx FPGA是什么

FPGA是什么?

- 導(dǎo)讀:本文系統(tǒng)講解了FPGA是什么及其結(jié)構(gòu)、原理、生產(chǎn)廠家等內(nèi)容,敬請閱讀~~ 一、FPGA是什么- -簡介 FPGA,是Field Programmable Gate Array的簡稱,中文名稱為現(xiàn)場可編程門陣列,是一種可編程器件,是在PAL(可編程邏輯陣列)、GAL(通用陣列邏輯)、CPLD(復(fù)雜可編程邏輯器件)等傳統(tǒng)邏輯電路和門陣列的基礎(chǔ)上發(fā)展起來的一種半定制電路,主要應(yīng)用于ASIC(專用集成電路)領(lǐng)域,既解決了半定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點。 二、FP

- 關(guān)鍵字: FPGA CPLD FPGA是什么

DSP是什么--DSP是神馬東東??

- 導(dǎo)讀:本文主要介紹的是DSP是什么,不懂得童鞋們快隨小編一起學(xué)習(xí)一下DSP到底是個神馬東東吧! 1.DSP是什么--簡介 DSP的全稱為Digital Signal Process,即數(shù)字信號處理技術(shù),DSP芯片即指能夠?qū)崿F(xiàn)數(shù)字信號處理技術(shù)的芯片。近年來,數(shù)字信號處理器(DSP)芯片已經(jīng)廣泛用于自動控制、圖像處理、通信技術(shù)、網(wǎng)絡(luò)設(shè)備、儀器儀表和家電等領(lǐng)域;DSP為數(shù)字信號處理提供了高效而可靠的硬件基礎(chǔ)。DSP芯片的內(nèi)部采用程序和數(shù)據(jù)分開的哈佛結(jié)構(gòu),具有專門的硬件乘法器,廣泛采用流水線操作,提供

- 關(guān)鍵字: DSP TMS320x24x DSP是什么

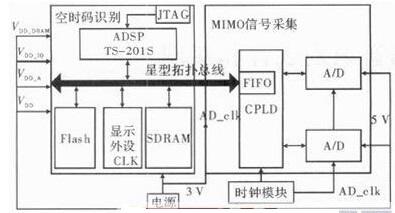

一種基于DSP的MIMO系統(tǒng)空時編碼盲識別方法

- 空時編碼(Space—Time Block Coding,STBC)是達到或接近MIMO無線信道容量的一種有效的編碼方式。空時編碼方式的盲識別是通信對抗領(lǐng)域需迫切研究的領(lǐng)域,其能夠為MIMO系統(tǒng)對抗技術(shù)提供基礎(chǔ)和技術(shù)支撐,具有重要的研究價值。 時滯相關(guān)算法是根據(jù)不同空時編碼的相關(guān)矩陣在不同時延統(tǒng)計下的差異性,采用逐級對比,實現(xiàn)對空時編碼方式的盲識別。擁有計算精度高,抗頻偏效果好等優(yōu)點。文中提出一種基于ADI公司DSP芯片TigerSHARCTS201S的空時編碼盲識別方案設(shè)計和實現(xiàn)。

- 關(guān)鍵字: DSP MIMO

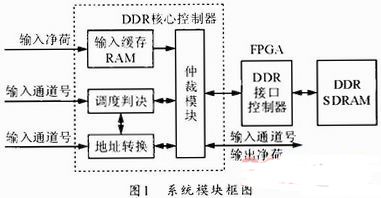

基于FPGA的MIMO視頻緩存器的設(shè)計與實現(xiàn)

- 隨著高速處理器的不斷發(fā)展,嵌入式系統(tǒng)應(yīng)用的領(lǐng)域越來越廣泛,高速大容量緩存器被廣泛應(yīng)用于音視頻系統(tǒng)中,然而專用的高速大容量緩存芯片價格過于昂貴,傳統(tǒng)SDRAM在帶寬上已經(jīng)逐漸無法滿足應(yīng)用要求,特別是對于多路數(shù)據(jù)多進多出時,兩者都無法很好的滿足要求,這里提出一種利用雙沿隨機動態(tài)存儲器(DDR SDRAM)結(jié)合外加專用電路的設(shè)計方案。 設(shè)計應(yīng)用在基于DVB-C的EOAM調(diào)制器系統(tǒng)中,該系統(tǒng)的基本要求能夠緩存集合多路視頻TS流的千兆IP數(shù)據(jù),并對IP數(shù)據(jù)進行多路高速分發(fā);輸入為2個千兆網(wǎng)口,輸出至RF射

- 關(guān)鍵字: FPGA MIMO

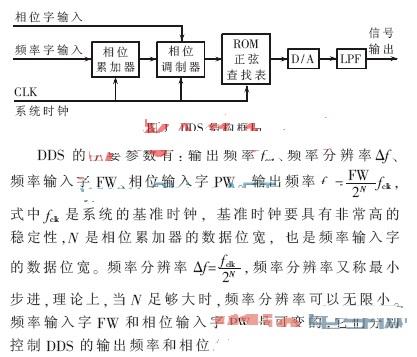

基于FPGA和虛擬儀器的DDS信號發(fā)生器的設(shè)計與實現(xiàn)

- 信號發(fā)生器是一種常用的信號源,廣泛應(yīng)用于通信、測量、科研等現(xiàn)代電子技術(shù)領(lǐng)域。信號發(fā)生器的核心技術(shù)是頻率合成技術(shù),主要方法有:直接模擬頻率合成、鎖相環(huán)頻率合成(PLL)、直接數(shù)字合成技術(shù)(DDS)。DDS 是開環(huán)系統(tǒng),無反饋環(huán)節(jié),輸出響應(yīng)速度快,頻率穩(wěn)定度高。因此直接數(shù)字頻率合成技術(shù)是目前頻率合成的主要技術(shù)之一。文中的主要內(nèi)容是采用FPGA 結(jié)合虛擬儀器技術(shù),進行DDS 信號發(fā)生器的開發(fā)[1-2]。 1 DDS 工作原理 圖1 是DDS 基本結(jié)構(gòu)框圖。以正弦波信號發(fā)生器為例,利用DDS 技術(shù)

- 關(guān)鍵字: FPGA DDS

基于FPGA+DDS的正弦信號發(fā)生器的設(shè)計

- 1971年,美國學(xué)者TIERNCY J、TADER C M和GOLD B在《A Digital Frequeney Synthesizer》一文中提出了以全數(shù)字技術(shù),從相位概念出發(fā)直接合成所需波形的一種新的頻率合成原理,稱之為直接數(shù)字頻率合成器DDS(Direct Digitial Frequency Synthesis)[1].這是頻率合成技術(shù)的一次重大革命,但限于當時微電子技術(shù)和數(shù)字信號處理技術(shù)的限制,DDS并沒有得到足夠的重視。隨著現(xiàn)代超大規(guī)模集成電路集成工藝的高速發(fā)展,數(shù)字頻率合成技術(shù)得到了質(zhì)

- 關(guān)鍵字: FPGA DDS

基于CPLD的系統(tǒng)硬件看門狗設(shè)計

- 引言 在以單片機、DSP等處理器為核心的數(shù)字系統(tǒng)中,看門狗是不可缺少的一部分,特別是在對可靠性要求極高的系統(tǒng)中,如箭上伺服控制器,由于箭體內(nèi)強弱電交叉使用,或者地面測試環(huán)境復(fù)雜多變,會產(chǎn)生諸多干擾和輻射。它們的沖擊會使CPU在執(zhí)行指令時的地址碼或操作碼發(fā)生變化,甚至將操作數(shù)作為操作碼執(zhí)行,導(dǎo)致程序跑飛。為使系統(tǒng)在規(guī)定時間內(nèi)重新正常工作,一種有效的措施是采用硬件看門狗技術(shù)。 本設(shè)計的最初思路來源:實現(xiàn)高可靠性數(shù)字伺服控制器軟、硬件看門狗的雙冗余設(shè)計要求,目前缺少軍品級國產(chǎn)化硬件看門狗器件,在

- 關(guān)鍵字: CPLD DSP

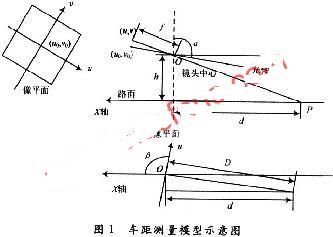

基于DSP和ARM9的汽車縱向碰撞預(yù)警系統(tǒng)設(shè)計

- 引言 利用圖像傳感器感知前方道路交通環(huán)境與障礙物位置,實現(xiàn)安全車距測量,對處于碰撞危險的汽車及時報警有利于減少交通事故,提高道路交通安全。由于理論計算的安全車距首先要以保障安全為前提,經(jīng)常與駕駛員在行駛過程中認可的安全車距有較大的出入,導(dǎo)致駕駛員對預(yù)警系統(tǒng)的不信任感,不利于系統(tǒng)的推廣使用。同時,作為安全輔助駕駛系統(tǒng)的處理平臺,PC機的體積、成本及功能的冗余性是應(yīng)用在車載系統(tǒng)中難以克服的瓶頸。 本文以圖像方式測量本車與前車的車距為基礎(chǔ),建立汽車縱向碰撞預(yù)警模型,解決理論計算的安全距離與駕駛員

- 關(guān)鍵字: DSP ARM9

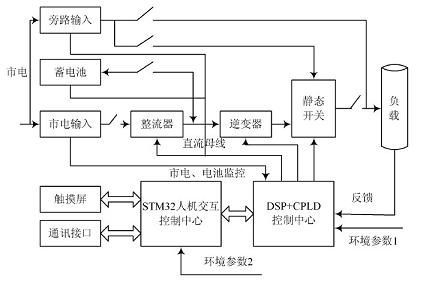

基于ARM7和DSP的逆變電源設(shè)計電路

- 引 言 在電氣智能化發(fā)展無處不在的今天, 無數(shù)用電場合離不開逆變電源系統(tǒng)( Inverted Pow er Supply System,IPS) 為現(xiàn)場設(shè)備提供穩(wěn)定的高質(zhì)量電源,特別在如通信機房、服務(wù)器工作站、交通樞紐調(diào)度中心、醫(yī)院、電力、工礦企業(yè)等對電源保障有苛刻要求的場合。許多IPS產(chǎn)品因遵循傳統(tǒng)設(shè)計而不符合或落后于現(xiàn)代電源理念,突出表現(xiàn)為控制模塊的單一復(fù)雜化,控制器芯片落后且控制任務(wù)繁重, 模擬閉環(huán)控制而得不到理想的監(jiān)控和反饋調(diào)節(jié)效果, 并由此帶來單個控制設(shè)備軟硬件設(shè)計上的隱患, 這對IP

- 關(guān)鍵字: ARM7 DSP

Altera加入工業(yè)互聯(lián)網(wǎng)聯(lián)盟,促進物聯(lián)網(wǎng)全球生態(tài)系統(tǒng)

- Altera公司今天宣布,公司加入工業(yè)互聯(lián)網(wǎng)聯(lián)盟(Industrial Internet Consortium,IIC),這一行業(yè)協(xié)作組織旨在促進物聯(lián)網(wǎng)(IoT)全球生態(tài)系統(tǒng)的發(fā)展。特別指出的是,Altera與聯(lián)盟成員在技術(shù)發(fā)展路線圖上一起工作,開發(fā)工業(yè)互聯(lián)網(wǎng),在這一智能設(shè)備和傳感器網(wǎng)絡(luò)上,數(shù)據(jù)通過不同的互聯(lián)協(xié)議進行交換,增強了多種終端市場應(yīng)用的性能。IoT的承諾是,這一智能連接網(wǎng)絡(luò)可支持企業(yè)開發(fā)“智能” 的新業(yè)務(wù)應(yīng)用,對資產(chǎn)和業(yè)務(wù)進行優(yōu)化、簡化,或者自動化現(xiàn)有流程。 工

- 關(guān)鍵字: Altera FPGA

fpga+dsp介紹

您好,目前還沒有人創(chuàng)建詞條fpga+dsp!

歡迎您創(chuàng)建該詞條,闡述對fpga+dsp的理解,并與今后在此搜索fpga+dsp的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對fpga+dsp的理解,并與今后在此搜索fpga+dsp的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司