基于FPGA+DDS的正弦信號發生器的設計

1971年,美國學者TIERNCY J、TADER C M和GOLD B在《A Digital Frequeney Synthesizer》一文中提出了以全數字技術,從相位概念出發直接合成所需波形的一種新的頻率合成原理,稱之為直接數字頻率合成器DDS(Direct Digitial Frequency Synthesis)[1].這是頻率合成技術的一次重大革命,但限于當時微電子技術和數字信號處理技術的限制,DDS并沒有得到足夠的重視。隨著現代超大規模集成電路集成工藝的高速發展,數字頻率合成技術得到了質的飛躍,它在相對帶寬、頻率轉換時間、相位連續性、正交輸出、高分辨率以及集成化等一系列性能指標方面,已遠遠超過了傳統頻率合成技術所能達到的水平。因此廣泛用于通信、宇航、遙控遙測、儀器儀表等各項電子領域[1-2].

本文引用地址:http://www.104case.com/article/272867.htm目前實現DDS的技術方案大致分為兩種,一是用專用的DDS芯片來實現。常用的DDS芯片有ADI公司的AD9xxx系列,如其中的AD9913,它具有高達100 MHz的模擬輸出,內部集成一個10位的D/A轉換器,頻率分辨率≥0.058 Hz,相調諧分辨率為0.022°[3].另一種是用FPGA來實現。可編程的FPGA器件具有內部資源豐富、處理速度快、可在系統內編程并有強大的EDA設計軟件支持等特點。因此,基于FPGA的設計相對于專用DDS芯片,可使電路設計更加靈活、提高系統的可靠性、縮短設計周期、降低成本。所以,采用FPGA設計的DDS系統具有很高的性價比。

1 DDS基本原理

直接數字頻率合成的理論依據是采樣定理,即先對一個完整周期的正弦波進行N點采樣,然后把采樣點存儲在ROM中構成一個查找表,頻率合成時,相位累加器在參考時鐘的作用下控制ROM中數據的輸出。ROM的輸出經過D/A轉換,將一個階梯化的信號(即采樣信號)通過一個理想的低通濾波器,就得到符合要求的模擬信號。

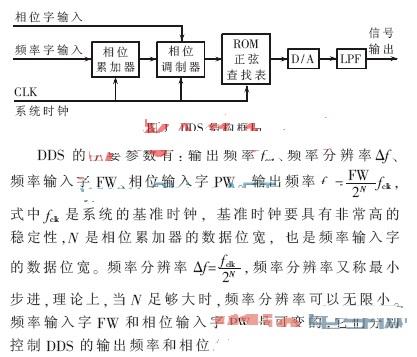

DDS的基本結構如圖1所示,主要由相位累加器、相位調制器、波形ROM查找表、DAC和低通濾波器(LPF)構成。其中相位累加器、相位調制器、波形ROM查找表是DDS結構中的數字部分,由于具有數控頻率合成的功能,又合稱為NCO(Numerically Controlled Oscillators)。

2 DDS波形發生器的系統設計

本系統分為軟件設計和硬件設計兩部分,軟件部分主要是基于FPGA的程序設計,硬件部分包括D/A轉換和低通濾波器設計。

2.1 VHDL程序設計

2.1.1定制波形數據文件

在設計DDS信號源之前,先建立一個儲存波形數據的ROM,儲存波形數據文件有。mif和。hex兩種格式。。mif和。hex格式的文件可以用Quartuas II建立,也可以用Quartuas II以外的編輯器設計,如MATLAB、C語言等。本系統的ROM文件一個周期有1 024個點的正弦波數據、10 bit地址線和10 bit數據線。

圖2 DDS的軟件設計框圖

低通濾波器相關文章:低通濾波器原理

負離子發生器相關文章:負離子發生器原理 數字濾波器相關文章:數字濾波器原理 離子色譜儀相關文章:離子色譜儀原理

評論