FPGA是什么

FPGA是英文Field Programmable Gate Array的縮寫,即現場可編程門陣列,它是在PAL、GAL、EPLD等可編程器件的基礎上進一步發(fā)展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。

本文引用地址:http://www.104case.com/article/272988.htm

FPGA——工作原理

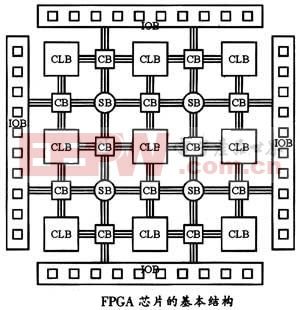

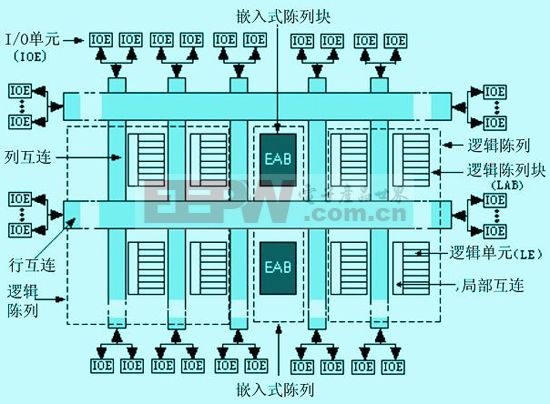

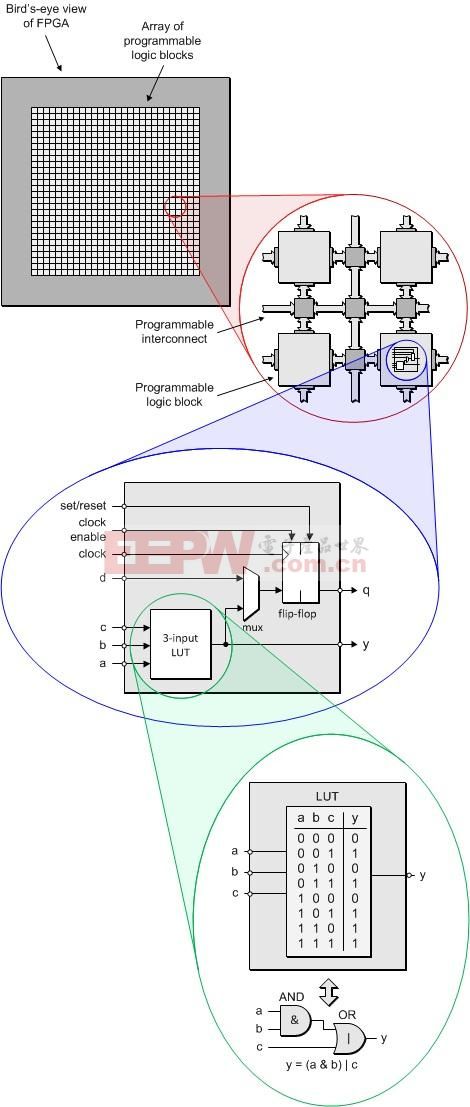

FPGA采用了邏輯單元陣列LCA(Logic Cell Array)這樣一個概念,內部包括可配置邏輯模塊CLB(Configurable Logic Block)、輸出輸入模塊IOB(Input Output Block)和內部連線(Interconnect)三個部分。 現場可編程門陣列(FPGA)是可編程器件。與傳統邏輯電路和門陣列(如PAL,GAL及CPLD器件)相比,FPGA具有不同的結構,FPGA利用小型查找表(16×1RAM)來實現組合邏輯,每個查找表連接到一個D觸發(fā)器的輸入端,觸發(fā)器再來驅動其他邏輯電路或驅動I/O,由此構成了既可實現組合邏輯功能又可實現時序邏輯功能的基本邏輯單元模塊,這些模塊間利用金屬連線互相連接或連接到I/O模塊。

FPGA的邏輯是通過向內部靜態(tài)存儲單元加載編程數據來實現的,存儲在存儲器單元中的值決定了邏輯單元的邏輯功能以及各模塊之間或模塊與I/O間的聯接方式,并最終決定了FPGA所能實現的功能,FPGA允許無限次的編程.

FPGA——特點

1)采用FPGA設計ASIC電路(專用集成電路),用戶不需要投片生產,就能得到合用的芯片。

2)FPGA可做其它全定制或半定制ASIC電路的中試樣片。

3)FPGA內部有豐富的觸發(fā)器和I/O引腳。

4)FPGA是ASIC電路中設計周期最短、開發(fā)費用最低、風險最小的器件之一。

5) FPGA采用高速CMOS工藝,功耗低,可以與CMOS、TTL電平兼容。

可以說,FPGA芯片是小批量系統提高系統集成度、可靠性的最佳選擇之一。

FPGA是由存放在片內RAM中的程序來設置其工作狀態(tài)的,因此,工作時需要對片內的RAM進行編程。用戶可以根據不同的配置模式,采用不同的編程方式。

加電時,FPGA芯片將EPROM中數據讀入片內編程RAM中,配置完成后,FPGA進入工作狀態(tài)。掉電后,FPGA恢復成白片,內部邏輯關系消失,因此,FPGA能夠反復使用。FPGA的編程無須專用的FPGA編程器,只須用通用的EPROM、PROM編程器即可。當需要修改FPGA功能時,只需換一片EPROM即可。這樣,同一片FPGA,不同的編程數據,可以產生不同的電路功能。因此,FPGA的使用非常靈活。

FPGA——內部結構

FPGA/CPLD結構由三大部分組成的。

1.一個二維的邏輯塊陣列,構成了PLD器件的邏輯組成核心。

2.輸入/輸出塊。

3.連接邏輯塊的可編程內部連線資源。連線資源:由各種長度的連線線段組成,其中有一些可編程的連接開關,它們用于邏輯塊之間、邏輯塊與輸入/輸出塊之間的連接。

Fpga的內部規(guī)模非常大,內部相當于幾千塊通用IC芯片。

FPGA——配置模式

FPGA的多種配置模式:

并行主模式為一片FPGA加一片EPROM的方式;

主從模式可以支持一片PROM編程多片FPGA;

串行模式可以采用串行PROM編程FPGA;

以及外設模式;

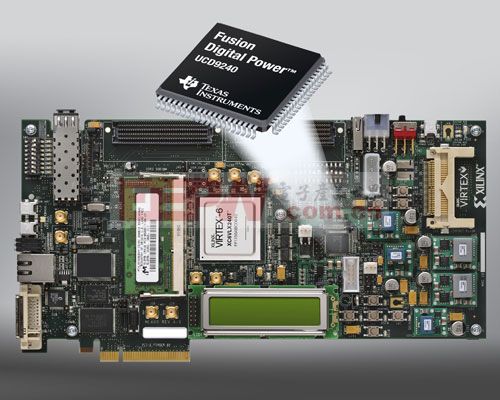

外設模式可以將FPGA作為微處理器的外設,由微處理器對其編程。 如何實現快速的時序收斂、降低功耗和成本、優(yōu)化時鐘管理并降低FPGA與PCB并行設計的復雜性等問題,一直是采用FPGA的系統設計工程師需要考慮的關鍵問題。如今,隨著FPGA向更高密度、更大容量、更低功耗和集成更多IP的方向發(fā)展,系統設計工程師在從這些優(yōu)異性能獲益的同時,不得不面對由于FPGA前所未有的性能和能力水平而帶來的新的設計挑戰(zhàn)。

例如,領先FPGA廠商Xilinx最近推出的Virtex-5系列采用65nm工藝,可提供高達33萬個邏輯單元、1,200個I/O和大量硬IP塊。超大容量和密度使復雜的布線變得更加不可預測,由此帶來更嚴重的時序收斂問題。此外,針對不同應用而集成的更多數量的邏輯功能、DSP、嵌入式處理和接口模塊,也讓時鐘管理和電壓分配問題變得更加困難。 幸運的是,FPGA廠商、EDA工具供應商正在通力合作解決65nm FPGA獨特的設計挑戰(zhàn)。不久以前,Synplicity與Xilinx宣布成立超大容量時序收斂聯合工作小組,旨在最大程度地幫助系統設計工程師以更快、更高效的方式應用65nm FPGA器件。設計軟件供應商Magma推出的綜合工具Blast FPGA能幫助建立優(yōu)化的布局,加快時序的收斂。FPGA的配置方式越來越多元化!

fpga相關文章:fpga是什么

可控硅相關文章:可控硅工作原理

評論