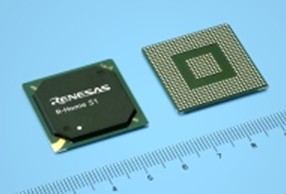

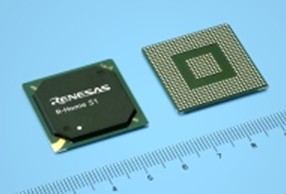

- 全球領先的高級半導體和解決方案的供應商瑞薩電子株式會社(TSE:6723,以下簡稱“瑞薩電子”)日前宣布推出適用于高端機頂盒(STB)的新款系統級芯片(SoC), R-Home S1,支持世界范圍的數字電視廣播接收和互聯網內容發布。

- 關鍵字:

瑞薩 SoC R-Home

- 摘要 介紹了Multibool的兩種實現方法。通過Xilinx Spartan-6 FPGA的Multiboot特性,允許用戶一次將多個配置文件下載入Flash中,根據不同時刻的需求,在不掉電重啟的情況下,從中選擇一個來重配置FPGA,實現不同功能,

- 關鍵字:

Xilinx-Spartan MultiBoot FPGA

- 硬件設計者已經開始在高性能DSP的設計中采用FPGA技術,因為它可以提供比基于PC或者單片機的解決方法快上10-100倍的運算量。以前,對硬件設計不熟悉的軟件開發者們很難發揮出FPGA的優勢,而如今基于C語言的方法可以讓

- 關鍵字:

FPGA C語言 計算 方案

- Linux操作系統的全稱是GNU/Linux,它是由GNU工程和Linux內核兩個部分共同組成的一個操作系統。該系統中所有組件的源代碼都是自由的,可以有效保護學習成果,因而在嵌入式領域得到了廣泛的應用。FPGA是英文Field Prog

- 關鍵字:

Linux FPGA 系統環境 驅動方案

- 摘要:為實現系統快速更新,在此設計了一種新的機器視頻解決方案,借助FPGA技術,實現視頻輸入端口與Gige Vision IP的使用以及系統與計算機主機的連接。設計方案中采用了新的Gige Vision標準及Gige Vision IP核,使系

- 關鍵字:

FPGA 機器視覺

- 摘要:衛星定位接收機中卷積碼譯碼即維特比譯碼器,在處理器中面臨占有資源較多、處理時間過長等問題,為了減少處理器資源的占用和提高處理速度,采用并行加比選蝶形單元的的方法,在FPGA平臺上用硬件描述語言設計一

- 關鍵字:

FPGA 性能 衛星導航 接收機

- 摘要:卡爾曼(Kalman)濾波計算精度和速度是工程應用中是否成功的決定性條件,為進一步提高Kalman濾波算法在更復雜的環境下使用的性能,并能夠同時滿足實時性和精度的要求,采用現場可編程邏輯陣列(FPGA)技術,設計了

- 關鍵字:

Kalman FPGA 濾波器 實現研究

- 摘要:介紹了如何利用FPGA設計TMS320C54x系列芯片與TMS62812ASDRAM之間的接口。這種接口方法適合于需要外擴...

- 關鍵字:

FPGA TMS320C54x SDRM

- 摘要:在級數的基礎上,設計一種基于FPGA的多項式運算器。利用該運算器可以在數字系統設計中更好地處理和應用各種函數。首先實現基于FPGA的多項式運算器,利用這個基本單元,進而實現了比較復雜的函數。經過驗證,該

- 關鍵字:

FPGA 運算器

- Achronix 半導體公司今日宣布了其 Speedster22i HD和HP產品系列的細節,它們是將采用英特爾22nm技術工藝制造的首批現場可編程門陣列(FPGA)產品。Speedster22i FPGA產品是業內唯一針對應用的高端FPGA,而且僅消耗28nm高端的FPGA一半的功率,成本也僅為它的一半。

- 關鍵字:

Achronix FPGA Speedster22i

- 摘要:通過賽靈思ISE及工具行為方式深入了解TS_clk約束,在FPGA設計方案中獲得高效率時序收斂。

- 關鍵字:

賽靈思 FPGA 201204

- 2012年3月19日,日本東京訊——全球領先的高級半導體和解決方案的供應商瑞薩電子株式會社(TSE:6723,以下簡稱“瑞...

- 關鍵字:

瑞薩電子 SoC

- 燦芯半導體日前宣布,開始面向客戶提供能滿足快速和可靠的RTL交付的新一代SoC集成平臺“Briliante”。根據客戶定制的目標,結合架構的復雜度,燦芯半導體能在1~3天內完成RTL設計以供綜合,包括自動生成測試案例以供驗證。此外,這個通用的平臺可以杜絕手工連接所帶來的風險,能通過簡單的、參數化的配置實施編程。

“Briliante”平臺不僅能通過AMBA AHB和APB的ARM標準總線來把基于ARM CortexTM-M0, Cortex-M3

- 關鍵字:

燦芯 SoC

- 1 基礎問題FPGA的基礎就是數字電路和HDL語言,想學好FPGA的人,建議床頭都有一本數字電路的書,不管是哪個版本的,這個是基礎,多了解也有助于形成硬件設計的思想。 在語言方面,建議初學者學習Verilog語言,VHDL語言

- 關鍵字:

FPGA 注意事項

- 摘要 以FPGA為核心,根據DDS原理設計數控信號源,采用VHDL語言實現各功能模塊。該信號源可輸出正弦渡、方波和三角波,輸出信號的頻率以數控方式調節,幅度連續可調。與傳統信號源相比,該信號源具有波形質量好、精度

- 關鍵字:

設計 實現 信號源 數控 FPGA DDS 基于

fpga soc介紹

您好,目前還沒有人創建詞條fpga soc!

歡迎您創建該詞條,闡述對fpga soc的理解,并與今后在此搜索fpga soc的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473