基于FPGA的Kalman濾波器實(shí)現(xiàn)研究

摘要:卡爾曼(Kalman)濾波計(jì)算精度和速度是工程應(yīng)用中是否成功的決定性條件,為進(jìn)一步提高Kalman濾波算法在更復(fù)雜的環(huán)境下使用的性能,并能夠同時(shí)滿足實(shí)時(shí)性和精度的要求,采用現(xiàn)場(chǎng)可編程邏輯陣列(FPGA)技術(shù),設(shè)計(jì)了Kaiman濾波算法在FPGA上的實(shí)現(xiàn)方案,選擇了一種可以同時(shí)滿足精度和實(shí)時(shí)性的方案進(jìn)行實(shí)現(xiàn),對(duì)算法中的矩陣相乘、狀態(tài)機(jī)的應(yīng)用以及資源分時(shí)復(fù)用等關(guān)鍵技術(shù)進(jìn)行了設(shè)計(jì)。通過與Matlab及DSP的計(jì)算結(jié)果相對(duì)比,驗(yàn)證了在FPGA內(nèi)實(shí)現(xiàn)Kalman濾波器的優(yōu)勢(shì)。

關(guān)鍵詞:FPGA;Kalman濾波器;IP核;實(shí)時(shí)性

Kalman濾波理論在20世紀(jì)60年代一經(jīng)提出,便得到了軍事、控制、通信等領(lǐng)域的極廣泛的應(yīng)用。它可以實(shí)現(xiàn)隨機(jī)干擾下的線性動(dòng)態(tài)系統(tǒng)的最優(yōu)估計(jì),目前Kalman濾波器的實(shí)現(xiàn)方式主要有兩種,一是在PC機(jī)上實(shí)現(xiàn),可以同時(shí)滿足計(jì)算精度和實(shí)時(shí)性的要求,但是PC機(jī)體積大,質(zhì)量重,成本高;二是通過DSP等芯片來實(shí)現(xiàn),用這種方式實(shí)現(xiàn)的Kalman濾波器雖然體積小,質(zhì)量輕,但是因其指令順序執(zhí)行的CPU架構(gòu),在系統(tǒng)復(fù)雜時(shí)無法滿足系統(tǒng)的實(shí)時(shí)性要求。隨著控制系統(tǒng)的復(fù)雜性的提高,系統(tǒng)的階次變大,如組合導(dǎo)航系統(tǒng)的濾波,其濾波的階次一般都要18階,如果對(duì)系統(tǒng)進(jìn)一步細(xì)化建模或增加其復(fù)雜性,其濾波階次可以達(dá)到幾十階。因此,Kalman濾波器在工程應(yīng)用中的實(shí)現(xiàn)遇到了系統(tǒng)體積、重量、成本和系統(tǒng)精度、速度等性能不能兼顧的問題。隨著現(xiàn)代電子技術(shù)的發(fā)展,F(xiàn)PGA具有系統(tǒng)結(jié)構(gòu)和邏輯單元靈活、集成度高以及適用范圍寬等特點(diǎn),可以很好地解決這個(gè)難題。因?yàn)镕PGA采用的是硬件并行算法,能很好的解決速度和實(shí)時(shí)性的問題,并且其具有靈活的可配置特性和優(yōu)良的抗干擾能力,使得FPGA構(gòu)成的數(shù)字信號(hào)處理系統(tǒng)非常易于修改、測(cè)試及硬件升級(jí)。隨著FPGA技術(shù)的不斷成熟,其內(nèi)嵌資源不斷豐富,硬核乘法器和塊RAM的數(shù)目不斷增長(zhǎng),使得FPGA實(shí)現(xiàn)復(fù)雜的數(shù)字信號(hào)處理算法變得更為簡(jiǎn)單和快速。因此,本文對(duì)FPGA技術(shù)和Kalman濾波算法進(jìn)行結(jié)合研究,探索Kalman濾波算法在FPGA中的實(shí)現(xiàn)方式并進(jìn)行性能驗(yàn)證,以對(duì)基于FPGA的Kalman濾波算法的工程實(shí)現(xiàn)提供參考。

1 Kalman濾波算法理論

Kalman濾波是在時(shí)域內(nèi)以信號(hào)的一、二階統(tǒng)計(jì)特性已知為前提、以均方誤差極小為判據(jù),能自動(dòng)跟蹤信號(hào)統(tǒng)計(jì)性質(zhì)的非平穩(wěn)變化,具有遞歸性質(zhì)的一種算法。它處理的對(duì)象是隨機(jī)系統(tǒng),并能正確估計(jì)出有用信號(hào)。設(shè)離散系統(tǒng)差分方程如下:

![]()

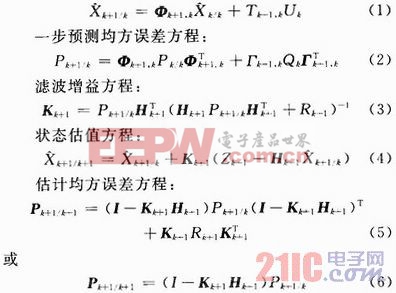

則Kalman濾波方程組如下:

狀態(tài)一步預(yù)測(cè)方程:

從式(1)~(6)可知,若利用傳統(tǒng)的處理器實(shí)現(xiàn)Kalman濾波算法,由于其指令執(zhí)行的順序性,至少需要分為5步來實(shí)現(xiàn),其中每一步還都需要進(jìn)行至少1次的加法和乘法等運(yùn)算,每次運(yùn)算都要順序執(zhí)行,其執(zhí)行速度和效率很低;如果利用FPGA來進(jìn)行Kalman濾波,根據(jù)其各步的邏輯關(guān)系,可以分為3步來實(shí)現(xiàn),即第一步計(jì)算狀態(tài)一步預(yù)測(cè)值![]() 和一步預(yù)測(cè)均方誤差Pk+1/k,第二步計(jì)算濾波增益Kk+1,第三步計(jì)算狀態(tài)最優(yōu)估值

和一步預(yù)測(cè)均方誤差Pk+1/k,第二步計(jì)算濾波增益Kk+1,第三步計(jì)算狀態(tài)最優(yōu)估值![]() 和估計(jì)均方誤差Pk+1/k+1。由此可知,利用FPGA技術(shù)可以實(shí)現(xiàn)Kalman濾波的并行計(jì)算,壓縮計(jì)算時(shí)間,提高解算速度。因此,對(duì)FPGA的Kalman濾波進(jìn)行研究開發(fā),可實(shí)現(xiàn)基于FPGA的快速Kalman濾波解算,滿足在對(duì)實(shí)時(shí)性要求更高的環(huán)境中使用。

和估計(jì)均方誤差Pk+1/k+1。由此可知,利用FPGA技術(shù)可以實(shí)現(xiàn)Kalman濾波的并行計(jì)算,壓縮計(jì)算時(shí)間,提高解算速度。因此,對(duì)FPGA的Kalman濾波進(jìn)行研究開發(fā),可實(shí)現(xiàn)基于FPGA的快速Kalman濾波解算,滿足在對(duì)實(shí)時(shí)性要求更高的環(huán)境中使用。

評(píng)論