EEPW首頁(yè) >>

主題列表 >>

fpga ip

fpga ip 文章 最新資訊

基于FPGA和DDS的信號(hào)源研究與設(shè)計(jì)

- 1引言直接數(shù)字頻率合成DDS(DirectDigitalSynthesizer)是基于奈奎斯特抽樣定理理論和現(xiàn)代器件生...

- 關(guān)鍵字: FPGA DDS 信號(hào)源 設(shè)計(jì)

高速流水線浮點(diǎn)加法器的FPGA實(shí)現(xiàn)

- 0引言現(xiàn)代信號(hào)處理技術(shù)通常都需要進(jìn)行大量高速浮點(diǎn)運(yùn)算。由于浮點(diǎn)數(shù)系統(tǒng)操作比較復(fù)雜,需要專用硬...

- 關(guān)鍵字: 高速流水線 浮點(diǎn)加法器 FPGA

基于FPGA的數(shù)據(jù)采集控制模塊的研究與設(shè)計(jì)

- 0引言數(shù)據(jù)采集和控制系統(tǒng)是對(duì)生產(chǎn)過(guò)程或科學(xué)實(shí)驗(yàn)中各種物理量進(jìn)行實(shí)時(shí)采集、測(cè)試和反饋控制的閉...

- 關(guān)鍵字: FPGA 數(shù)據(jù)采集

FC-AL系統(tǒng)中FPGA的彈性緩存設(shè)計(jì)

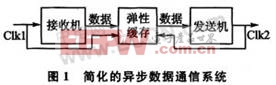

- 引 言一個(gè)簡(jiǎn)化的異步數(shù)據(jù)通信系統(tǒng)如圖1所示。接收機(jī)端從接收到的來(lái)自串行鏈路的比特流中提取時(shí)鐘信號(hào)Clk1,作為其工作時(shí)鐘源;而發(fā)送機(jī)端采用本地晶振和鎖相環(huán)產(chǎn)生的時(shí)鐘Clk2,作為其工作時(shí)鐘源。接收機(jī)在時(shí)鐘Clk1的

- 關(guān)鍵字: 設(shè)計(jì) 彈性 FPGA 系統(tǒng) FC-AL

Altium推出采用Altera Cyclone III FPGA 的NanoBoard 3000

- 繼去年 9 月發(fā)布基于 NanoBoard 3000 的快速原型設(shè)計(jì)全新方案后,Altium日前又宣布推出采用 Altera Cyclone III® FPGA 的最新 NanoBoard 3000,從而進(jìn)一步擴(kuò)展了這一理念。 新的開(kāi)發(fā)板為電子設(shè)計(jì)人員繼續(xù)提供相同的軟硬件以及 NanoBoard 3000 可以直接使用的免專利費(fèi) IP,所不同的是,在其內(nèi)核中提供了具有 Altera 高性價(jià)比 Cyclone III® FPGA 電源。 電子設(shè)計(jì)人員采用 NanoBoard

- 關(guān)鍵字: Altium FPGA NanoBoard

低功耗FPGA電子系統(tǒng)優(yōu)化方法

- 首先與實(shí)測(cè)系統(tǒng)功耗進(jìn)行對(duì)比,驗(yàn)證了Xilinx公司ISE軟件包中FPGA功耗估算工具XPower的準(zhǔn)確性。然后對(duì)FPGA設(shè)計(jì)中影響系統(tǒng)功耗的幾個(gè)相互關(guān)聯(lián)的參數(shù)進(jìn)行取樣,通過(guò)軟件估算不同樣點(diǎn)下的系統(tǒng)功耗,找到功耗最低的取樣點(diǎn),得到最佳設(shè)計(jì)參數(shù),從而達(dá)到優(yōu)化系統(tǒng)設(shè)計(jì)的目的。實(shí)驗(yàn)中通過(guò)這種方法,在一個(gè)FPGA讀寫(xiě)SRAM的系統(tǒng)中,在單位時(shí)間讀寫(xiě)操作數(shù)固定的條件下,選取了讀寫(xiě)頻率與讀寫(xiě)時(shí)間占空比這兩個(gè)參數(shù)來(lái)優(yōu)化系統(tǒng)功耗。最終測(cè)試數(shù)據(jù)證明了該方法的正確性。

- 關(guān)鍵字: FPGA 低功耗 電子 系統(tǒng)優(yōu)化

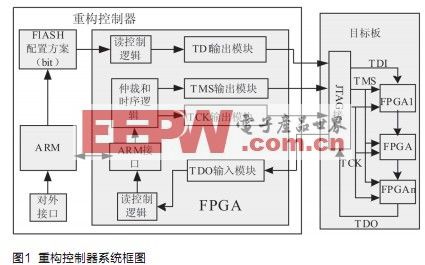

基于JTAG邊界掃描方式的重構(gòu)控制器的設(shè)計(jì)

- 為充分利用硬件資源,滿足不同的應(yīng)用需求,本文提出了一種基于JTAG邊界掃描模式配置的重構(gòu)控制器,詳細(xì)介紹控制器的硬件實(shí)現(xiàn)以及配置流程,該控制器通過(guò)模擬JTAG接口時(shí)序及TAP狀態(tài)機(jī)的功能,實(shí)現(xiàn)在系統(tǒng)配置目標(biāo)可編程器件。

- 關(guān)鍵字: FPGA TAP狀態(tài)機(jī) JTAG邊界掃描 重構(gòu) 201001

FPGA的甜蜜時(shí)光

- 隨著2010年的來(lái)臨,當(dāng)今的全球電子公司紛紛做出明智而審慎的研發(fā)投資決定,以便借助創(chuàng)新的新產(chǎn)品,快速抓住新的市場(chǎng)機(jī)遇。FPGA越來(lái)越多地成為這些公司成功的關(guān)鍵。除了少數(shù)可超大批量生產(chǎn)的商品外,應(yīng)用ASIC的高成本和高風(fēng)險(xiǎn)無(wú)法讓絕大多數(shù)的商品贏利;現(xiàn)在面臨著加速替代ASIC所帶來(lái)的機(jī)遇,這主要體現(xiàn)在以下不同方面:芯片體系結(jié)構(gòu),也就是能夠推出某種架構(gòu)和相關(guān)的I/O,而且,密度和性能還能夠達(dá)到一定水平,從而可以替代ASIC的功能。 軟件在加速替代ASIC過(guò)程中也扮演了重要角色。高效的軟件和設(shè)計(jì)工具大大提高了

- 關(guān)鍵字: 賽靈思 FPGA ASIC 摩爾定律

臺(tái)積電年中將為Altera試產(chǎn)28nm制程FPGA芯片

- 據(jù)業(yè)者透露,臺(tái)積電公司將于今年中期開(kāi)始為Altera公司生產(chǎn)28nm制程FPGA芯片產(chǎn)品。這種FPGA芯片將集成有28Gbps收發(fā)器,產(chǎn)品面向云計(jì)算,在線存儲(chǔ)以及移動(dòng)視頻等應(yīng)用,Altera公司兩年前曾推出該系列產(chǎn)品的 40nm制程版本。臺(tái)積電還宣布其28nm制程將為全代制程(full node:即制程升級(jí)時(shí)需要對(duì)芯片電路進(jìn)行重新設(shè)計(jì)),而且年內(nèi)其28nm制程還將具備可按客戶的需求制作出HKMG(High-K絕緣層+金屬柵極)或SiON(SiON絕緣層+硅柵極)這兩種不同柵極結(jié)構(gòu)的能力. 臺(tái)積電

- 關(guān)鍵字: 臺(tái)積電 28nm FPGA Altera

我國(guó)軌道交通的視頻監(jiān)控發(fā)展與應(yīng)用解析

- 隨著我國(guó)的經(jīng)濟(jì)高速發(fā)展,人員、交通工具數(shù)量急劇增加,城市公共交通的狀況日益惡化,一個(gè)突發(fā)事件就會(huì)引發(fā)嚴(yán)重的...

- 關(guān)鍵字: 軌道交通 視頻監(jiān)控 IP IPSAN存儲(chǔ)

理解FPGA 中的壓穩(wěn)態(tài)

- 理解FPGA 中的壓穩(wěn)態(tài) 本白皮書(shū)介紹FPGA 中的壓穩(wěn)態(tài),為什么會(huì)出現(xiàn)這一現(xiàn)象,它是怎樣導(dǎo)致設(shè)計(jì)失敗的。介紹怎樣計(jì)算壓穩(wěn)態(tài)MTBF,重點(diǎn)是對(duì)結(jié)果造成影響的各種器件和設(shè)計(jì)參數(shù)。

引言

當(dāng)信號(hào)在不相關(guān)或者異步時(shí)鐘域 - 關(guān)鍵字: FPGA 壓穩(wěn)態(tài)

fpga ip介紹

您好,目前還沒(méi)有人創(chuàng)建詞條fpga ip!

歡迎您創(chuàng)建該詞條,闡述對(duì)fpga ip的理解,并與今后在此搜索fpga ip的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)fpga ip的理解,并與今后在此搜索fpga ip的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司