- FPGA MC-CDMA 基帶系統 移動通信 摘 要: MIMO技術、多載波技術與鏈路自適應技術是未來移動通信系統最值得關注的幾種物理層技術。MIMO技術在提高系統頻譜利用率方面性能卓越,多載波CDMA技術則能有效地對抗頻率選

- 關鍵字:

CDMA 系統 設計 MC MIMO FPGA 空域 復用 基于

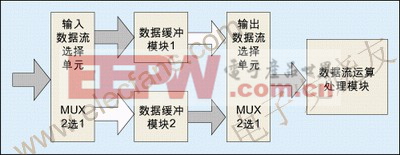

- FPGA/CPLD設計思想與技巧, 本文討論的四種常用FPGA/CPLD設計思想與技巧:乒乓操作、串并轉換、流水線操作、數據接口同步化,都是FPGA/CPLD邏輯設計的內在規律的體現,合理地采用這些設計思想能在FPGA/CPLD設計工作中取得事半功倍的效果。

- 關鍵字:

技巧 設計思想 FPGA/CPLD

- 摘要:提出了一種基于FPGA 的數字幅頻均衡功率放大器的設計方案。系統在完成基于AD620前級小信號放大電路設計的基礎上,分析了阻帶網絡的幅頻特性;結合分析結果與FIR 濾波算法給出了相應的濾波器組成方案。后級功

- 關鍵字:

FPGA 數字 幅頻均衡 方案

- 摘要:現代測試領城中,經常需要信號發生器提供多種多樣的的測試信號去檢驗實際電路中存在的設計問題。傳統的信號發生器多采用模擬電路搭建。以正弦波信號發生器為例,結合DDS直接數字合成技術,基于FPGA設計其他外圍

- 關鍵字:

FPGA 正弦波信號 發生器

- 多相濾波是實現數字下變頻及數字相干檢波的關鍵技術,是雷達、聲納和通信等系統中為數字信號處理提供高質量的正交信號的有效手段。文中討論了多相濾波的基本原理,給出了采用多相濾波的方法對中頻帶限信號處理的仿真分析,并結合一款脈沖壓縮雷達中頻數字化接收機的實現方案進行工程驗證,結果表明,在技術指標上可有效克服正交通道不一致問題,具有較高的應用價值。

- 關鍵字:

FPGA 多相濾波 數字 相干檢波

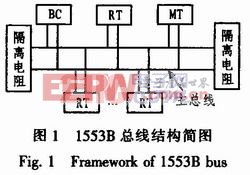

- 基于DSP的1553B總線系統設計與實現,摘要:在研究1553B總線協議特點的基礎上,提出了一種基于DSP的1553B總線接口設計方案.詳細描述了硬件電路的實現及軟件驅動程序的編寫。在電路中采用DSPTMS320F2812為核心處理單元。BU-64843為1553B協議執行元件,采

- 關鍵字:

DSP FPGA

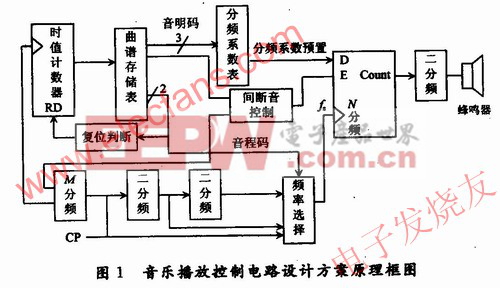

- 基于FPGA的音樂播放控制電路設計, 隨著電子技術發展,電子電路的形式趨向復雜化,面對這一狀況,人們已經清醒地認識到,要分析和設計復雜的電子系統人工的方法已不適用。依靠傳統的實驗教學已遠不能滿足社會對高新技術人才的培養需要。本文就一個

- 關鍵字:

控制 電路設計 播放 音樂 FPGA 基于

- 基于FMC標準的FPGA夾層卡I/O設計, 面對似乎層出不窮的新 I/O 標準,目前嵌入式系統設計人員繼續依靠 FPGA 來部署系統日益重要的外部 I/O 接口,這點絲毫不足為奇。FPGA 可提供大量可配置的 I/O,能在適當 IP 基礎上支持幾乎無限多種高度復雜的 I/O

- 關鍵字:

I/O 設計 夾層 FPGA FMC 標準 基于

- 采用90nm工藝制造的DDR3 SDRAM存儲器架構支持總線速率為600 Mbps-1.6 Gbps (300-800 MHz)的高帶寬,工作電壓低至1.5V,因此功耗小,存儲密度更可高達2Gbits。該架構無疑速度更快,容量更大,單位比特的功耗更低,但問

- 關鍵字:

SDRAM FPGA DDR3 存儲器

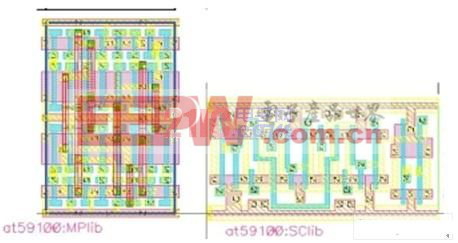

- 摘 要: 基于FPGA芯片Stratix II EP2S60F672C4設計了一個適用于寬帶數字接收機的帶寬可變的數字下變頻器(VB-DDC)。該VB-DDC結合傳統數字下變頻結構與多相濾波結構的優點,實現了對輸入中頻信號的高效高速處理,同

- 關鍵字:

FPGA 寬帶數字 接收機 帶寬

- 隨著通信協議的發展及多樣化,協議處理部分PE在硬件轉發實現方面,普遍采用現有的商用芯片NP(Network Processor,網絡處理器)來完成,流量管理部分需要根據系統的需要進行定制或采用商用芯片來完成。在很多情況下NP

- 關鍵字:

FPGA Core 定制

- 基于ARM的可定制MCU可承擔FPGA的工作,如今的產品生命周期可能短至六個月,因此在這種情況下要想取得定制ASIC的低成本、低功耗和高性能優勢幾乎是不可能的。定制ASIC的設計周期通常要一年左右,這通常要比終端產品的生命周期還要長。另外,標準單元ASIC還

- 關鍵字:

ARM MCU FPGA

- 因應MCU成長快速及程序數據儲存需要,MCU內嵌Flash內存設計成為主流趨勢,MCU大廠也紛紛以購并或結盟掌握內嵌Flash的相關IP與制程技術。本文將探討內嵌FlashIP制程技術,為下一代FlashMCU帶來的技術變革。

- 關鍵字:

MCU Flash

- DDS(DirectDigitalFreqiaencySynthesizers)廣泛應用于雷達系統、數字通信、電子對抗、電子測量等民...

- 關鍵字:

DDFS DDWS FPGA

flash fpga介紹

您好,目前還沒有人創建詞條flash fpga!

歡迎您創建該詞條,闡述對flash fpga的理解,并與今后在此搜索flash fpga的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473