基于FPGA的數字幅頻均衡功率放大器的解決方案

摘要:提出了一種基于FPGA 的數字幅頻均衡功率放大器的設計方案。系統在完成基于AD620前級小信號放大電路設計的基礎上,分析了阻帶網絡的幅頻特性;結合分析結果與FIR 濾波算法給出了相應的濾波器組成方案。后級功率放大電路采用分立MOS 管實現。

本文引用地址:http://www.104case.com/article/191486.htm在現代通信系統中,碼間干擾是制約通信質量的重要因素。為了減小碼間干擾,需要對信道進行適當的補償,以減小誤碼率,提高通信質量,接收機中能夠補償或減小接收信號碼間干擾的補償器稱為均衡器。。本文提出了一種基于FPGA 的數字幅頻均衡功率放大器的解決方案。

1 系統總體設計

本文設計了一種數字信號幅頻均衡功率放大器的實現方案。設計主要由四個模塊組成。分別為小信號放大,帶阻網絡衰減,數字信號幅度的均衡處理以及功率放大。其中小信號放大部分由精密度高、噪音系數小的運算放大器AD620 實現;數字信號處理部分以FPGA 為處理核心,輔助以A/D、D/A 模塊進行模擬信號和數字信號的轉換;末級功放電路采用分立的MOS管來實現。

2 硬件電路設計

2.1 前置放大電路設計

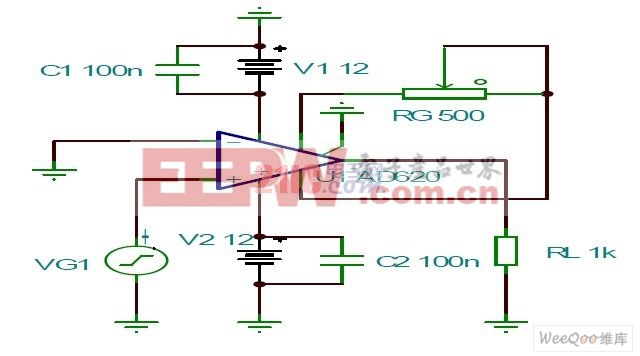

前置小信號放大器利用低功耗高精度的儀表運放AD620[3],在運放1 管腳和8 管腳之間介入可變電阻來實現增益可控,以滿足題目中要求放大倍數不小于400 倍。前級放大電路如圖1所示。根據AD620 的內部結構,其增益表達式如下:

Au=(R1+R2)/RG+1=49.4k Ω / RG+1,其中,RG 的單位為k Ω 。

圖1 AD620 放大電路

2.2 帶阻網絡的計算

阻帶網絡電路(詳見賽題)。根據基爾霍夫定律:

I1=I2+I3 (1)

U1= I1Z1+I3Z3 (2)

I3Z3= I2Z2+ U2 (3)

U2= I2RL=600*I2 (4)

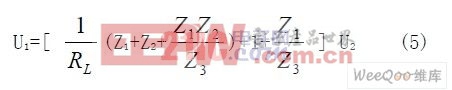

由式(1)(2)(3)(4)得U1 、U2 的關系:

(其中,Z1、 Z2 、Z3 分別為各諧振網絡的總阻抗)

評論