EEPW首頁(yè) >>

主題列表 >>

fir ip

fir ip 文章 最新資訊

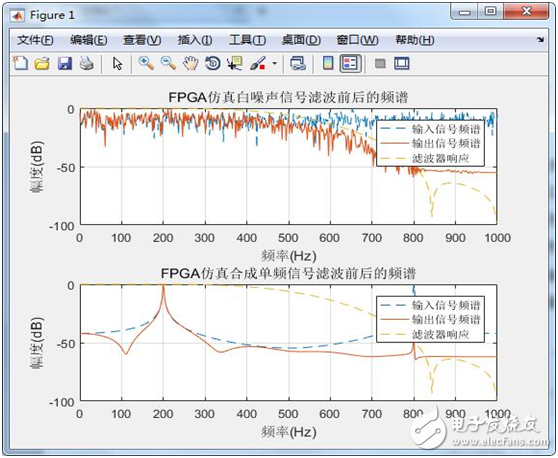

基于MATLAB與QUARTUS II的 FIR濾波器設(shè)計(jì)與驗(yàn)證

- 1 引言

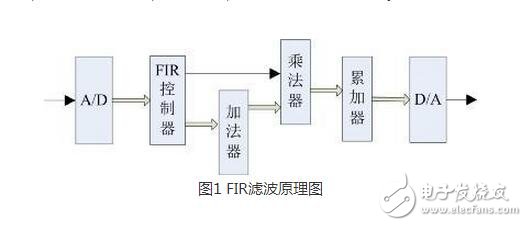

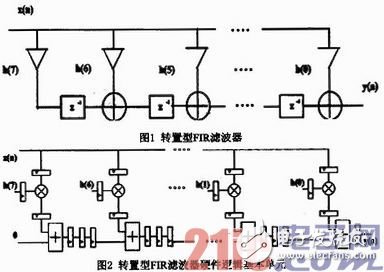

FIR數(shù)字濾波器能夠滿足濾波器對(duì)幅度和相位特性的嚴(yán)格要求,避免模擬濾波器的溫漂和噪聲等問(wèn)題,具有精確的線性相位、易于硬件實(shí)現(xiàn)和系統(tǒng)穩(wěn)定等優(yōu)點(diǎn),可廣泛應(yīng)用于現(xiàn)代電子通信系統(tǒng)。實(shí)際信號(hào)處理應(yīng)用往往 - 關(guān)鍵字: QUARTUS MATLAB FIR 濾波器設(shè)計(jì)

Gartner:今年半導(dǎo)體創(chuàng)業(yè)公司籌資逾7.5億美元

- 據(jù)國(guó)外媒體報(bào)道,美國(guó)市場(chǎng)研究公司Gartner表示,全球半導(dǎo)體創(chuàng)業(yè)公司今年以來(lái)總計(jì)籌集了超過(guò)7.5億美元資金,但其中約四分之一的投資來(lái)自于大型半導(dǎo)體公司旗下風(fēng)投部門等戰(zhàn)略投資者。 Gartner指出,在過(guò)去的這一年,風(fēng)投公司主要青睞投資后期創(chuàng)業(yè)公司,與去年相比,今年獲得投資的創(chuàng)業(yè)公司數(shù)量明顯下降。每家公司獲得的投資金額最高為4000萬(wàn)美元,平均為1430萬(wàn)美元。 Gartner表示,在獲得投資的創(chuàng)業(yè)公司中,70%為無(wú)晶圓廠芯片公司,14%為EDA(電子設(shè)計(jì)自動(dòng)化)公司,7%為IP公司,5%

- 關(guān)鍵字: 半導(dǎo)體 IP OEM

基于DSP/BIOS的FIR數(shù)字濾波器設(shè)計(jì)與實(shí)現(xiàn)

- 用可編程DSP器件實(shí)現(xiàn)數(shù)字濾波,通過(guò)修改濾波器參數(shù)可方便地改變?yōu)V波器的特性。以TMS320F2812數(shù)字信號(hào)處理器為核心,將濾波器算法作為DSP/BIOS的任務(wù)來(lái)實(shí)現(xiàn),可方便地實(shí)現(xiàn)多任務(wù)系統(tǒng)。詳細(xì)介紹一種基于DSP/B10S的軟件開發(fā)過(guò)程,并在DSK2812平臺(tái)上實(shí)現(xiàn)數(shù)字濾波器的開發(fā)實(shí)例,對(duì)需進(jìn)行數(shù)字信號(hào)處理的多任務(wù)軟件開發(fā)具有一定的參考價(jià)值。

- 關(guān)鍵字: 設(shè)計(jì) 實(shí)現(xiàn) 濾波器 數(shù)字 DSP/BIOS FIR 基于

基于DSP Builder的16階FIR濾波器實(shí)現(xiàn)

- 現(xiàn)場(chǎng)可編程門陣列(FPGA)器件廣泛用于數(shù)字信號(hào)處理領(lǐng)域.而使用VHDL或VerilogHDL語(yǔ)言進(jìn)行設(shè)計(jì)的難度較大。提出一種采用DSP Builder實(shí)現(xiàn)FIR濾波器的設(shè)計(jì)方案,按照Matlab/Simulink/DSP Builder/Modelsim/QuartusⅡ的設(shè)計(jì)流程,設(shè)計(jì)一個(gè)16階的FIR低通濾波器,并完成了軟硬件的仿真與驗(yàn)證。結(jié)果表明,該方法簡(jiǎn)單易行,可滿足設(shè)計(jì)要求,它驗(yàn)證了采用DSP Builder實(shí)現(xiàn)濾波器設(shè)計(jì)的獨(dú)特優(yōu)勢(shì)。

- 關(guān)鍵字: Builder DSP FIR 濾波器

FIR帶通濾波器的FPGA實(shí)現(xiàn)

- 為設(shè)計(jì)一個(gè)項(xiàng)目可用的FIR數(shù)字帶通濾波器,采用Matlab/Simulink軟件中DSPBulider強(qiáng)大的算法模塊設(shè)計(jì)工具,結(jié)合Altera公司的FPGA開發(fā)板實(shí)現(xiàn)FIR數(shù)字帶通濾波器的系統(tǒng)集成、RTL級(jí)仿真、綜合編譯、下載等設(shè)計(jì)流程,并對(duì)正弦信號(hào)進(jìn)行濾波,結(jié)果下載到開發(fā)板上用示波器觀測(cè),達(dá)到了預(yù)期的濾波效果和目的。基于DSPBuilder完成系統(tǒng)建模,省去了復(fù)雜的VHDL編程,還可針對(duì)具體模塊進(jìn)行參數(shù)設(shè)置從而適應(yīng)不同的濾波需求。該方法實(shí)現(xiàn)簡(jiǎn)單、可靠,還可類推實(shí)現(xiàn)其他復(fù)雜的嵌入式系統(tǒng)設(shè)計(jì)。

- 關(guān)鍵字: FPGA FIR 帶通濾波器

Avago宣布向Juniper Networks提供關(guān)鍵知識(shí)產(chǎn)權(quán)IP

- Avago Technologies(安華高科技)今日宣布,公司提供的關(guān)鍵知識(shí)產(chǎn)權(quán)(IP, Intellectual Property)已經(jīng)幫助Juniper Networks公司成功進(jìn)行高性能硅芯片器件產(chǎn)品的開發(fā),這些新設(shè)計(jì)為帶來(lái)Juniper公司MX-3D平臺(tái)Junos® Trio芯片組的一部分。Avago為提供通信、工業(yè)和消費(fèi)性等應(yīng)用模擬接口元器件之全球領(lǐng)導(dǎo)廠商。 每個(gè)器件都擁有接近100個(gè)SerDes串行/解串器通道,并且可以推動(dòng)松散背板通道和多重背板連接器,除了展現(xiàn)出同級(jí)產(chǎn)品最

- 關(guān)鍵字: Avago 硅芯片 IP

賽靈思與ARM公司共同宣布合作開發(fā)計(jì)劃

- 全球可編程邏輯解決方案領(lǐng)導(dǎo)廠商賽靈思公司與ARM公司宣布正式開展合作,在賽靈思FPGA中應(yīng)用ARM處理器與互聯(lián)技術(shù)。賽靈思公司目前已經(jīng)開始采用ARM Cortex處理器IP,利用性能優(yōu)化的ARM數(shù)字單元庫(kù)(cell library)和嵌入式存儲(chǔ)器,為未來(lái)的可編程平臺(tái)提供支持。此外,兩家公司還共同對(duì)下一代ARM® AMBA®互聯(lián)技術(shù)進(jìn)行定義,以增強(qiáng)并優(yōu)化FPGA架構(gòu)。 兩大公司的合作, 意味著賽靈思致力于采用全線ARM技術(shù),并充分利用ARM處理器的巨大優(yōu)勢(shì)為客戶和生態(tài)系統(tǒng)開發(fā)人員提

- 關(guān)鍵字: Xilinx FPGA Cortex IP

GSM 協(xié)會(huì)推出國(guó)際號(hào)碼可攜帶登記服務(wù)

- GSM 協(xié)會(huì) (GSMA) 今天宣布推出 PathFinder Number Portability Discovery 服務(wù)。這是一種由 GSM 協(xié)會(huì)管理,由 Neustar, Inc. 經(jīng)營(yíng)的服務(wù)。這項(xiàng)新服務(wù)旨在成為全球號(hào)碼可攜帶性的最先進(jìn)解決方案,它面向的是全球22億個(gè)受到號(hào)碼可攜帶性影響的電話號(hào)碼,而這一數(shù)字預(yù)計(jì)還將快速上升。號(hào)碼可攜帶 (Number Portability) 目前已在全球超過(guò)52個(gè)國(guó)家實(shí)現(xiàn),而且預(yù)計(jì)2010年年底之前還會(huì)在中國(guó)和印度等更多國(guó)家推行。這項(xiàng)服務(wù)還將集合全球幾乎所

- 關(guān)鍵字: GSM IP PathFinder

基于PSO的FIR數(shù)字濾波器設(shè)計(jì)

- 有限沖激響應(yīng)(FIR)數(shù)字濾波器的設(shè)計(jì)實(shí)質(zhì)是一個(gè)多參數(shù)優(yōu)化的問(wèn)題,而傳統(tǒng)的一些優(yōu)化設(shè)計(jì)方法,如遺傳算法、神經(jīng)網(wǎng)絡(luò)法等,存在算法復(fù)雜,收斂速度慢,效果不明顯等缺點(diǎn)。提出一種改進(jìn)粒子群優(yōu)化算法(IMPSO)的FIR數(shù)字濾波器設(shè)計(jì)。該方法首先根據(jù)粒子聚合度情況引入變異思想,克服PSO算法容易早熟的毛病,對(duì)算法進(jìn)行改進(jìn),然后利用改進(jìn)的IMPSO搜索濾波器參數(shù)的最優(yōu)解,對(duì)FIR濾波器進(jìn)行優(yōu)化設(shè)計(jì)。實(shí)例設(shè)計(jì)FIR數(shù)字低通、帶通濾波器,仿真結(jié)果表明,該方法具有算法簡(jiǎn)單,收斂速度快,魯棒性好等優(yōu)點(diǎn)。

- 關(guān)鍵字: PSO FIR 數(shù)字 濾波器設(shè)計(jì)

基于Actel FPGA的PWM IP的應(yīng)用

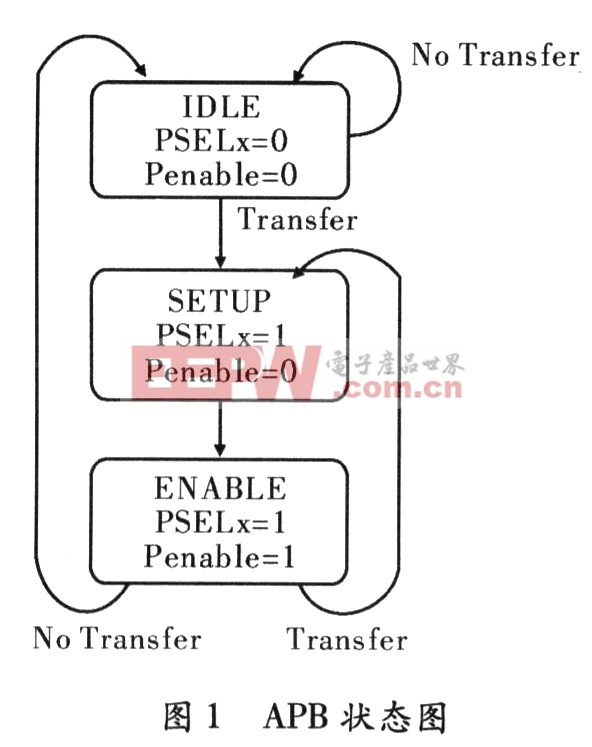

- 脈沖寬度調(diào)制(PWM)是英文“Pluse Width Modulation”的縮寫,簡(jiǎn)稱脈寬調(diào)制。它是利用微處理器的數(shù)字輸出來(lái)對(duì)模擬電路進(jìn)行控制的一種非常有效的技術(shù),根據(jù)相應(yīng)的載荷的變化來(lái)調(diào)制晶體管柵極或基極的偏置,來(lái)實(shí)現(xiàn)開關(guān)穩(wěn)壓電源輸出晶體管或晶體管導(dǎo)通時(shí)間的改變。這種方式能使電源的輸出電壓在工作條件變化時(shí)保持恒定,廣泛應(yīng)用于測(cè)量、通信、功率控制與變化等許多領(lǐng)域。 Actel公司免費(fèi)提供PWM IP核:CorePWM。CorePWM是基于APB總線形式的,它的優(yōu)點(diǎn)是可以

- 關(guān)鍵字: Actel FPGA PWM IP 200909

fir ip介紹

您好,目前還沒有人創(chuàng)建詞條fir ip!

歡迎您創(chuàng)建該詞條,闡述對(duì)fir ip的理解,并與今后在此搜索fir ip的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)fir ip的理解,并與今后在此搜索fir ip的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司