基于SoC的音頻IP模塊設計

隨著集成電路設計技術和深亞微米制造技術的發展,集成電路已進入了片上系統時代。由于SoC結構極其復雜,對于設計者而言,數百萬門規模的系統級芯片設計不可能一切從頭開始,隨著集成電路設計技術的發展,IP核的開發己成為不可忽視的發展趨勢,它的出現為SoC的實現和發展提供了基礎。IP稱之為知識產權,它可以認為是封裝在硬件設計中的可重復利用的軟件,就功能而言,IP核可以定義為SoC的基本電路功能塊又稱為內核,可由用戶或專用IC公司或獨立的公司開發而成,IP核的顯著特點是具有重用性。鑒于SoC系統設計者很難獨自開發、維護和移植所有必須的IP核,所以在Soc設計中必然要用到第3方的IP核,當IP核被轉移到用戶設計與制造工藝中時,IP核被重復利用了,具有自主知識產權的IP核的復用是Soc設計中解決設計層次、產品成本、設計周期和降低風險的關鍵環節是SoC設計中的關鍵技術。IP核重復利用可以提高設計能力,節省設計人員可以縮短上市時間,更好的利用現有的工藝技術,降低成本。基于此筆者設計了基于SoC的音頻接口IP模塊。

1 APB與IIS總線

APB(Advanced Peripheral Bus)是AMBA(Advanced Microcontrollel Bus Architectrure)組成部分,是用于低功耗和減少接口復雜度而設計的。APB用于帶寬,低速,低性能要求,無管線操作的外圍設備。APB總線操作包括Setup和Enable兩個狀態。其中APB讀操作只需在Enable狀態數據有效,寫操作要求寫數據在整個寫操作期間保持有效。

APB協議規定每個傳輸只與時鐘上升沿相關。這就使APB外圍設備很容易被集成在設計之中,特點如下:

(1)在高頻操作的性能改進;

(2)獨立的脈沖時鐘;

(3)靜態時鐘分析比較簡單,因為用單時鐘沿觸發;

(4)自測試邏輯插入沒有特別的條件需要考慮;

(5)在ASIC庫中有性能很好的上升沿寄存器;

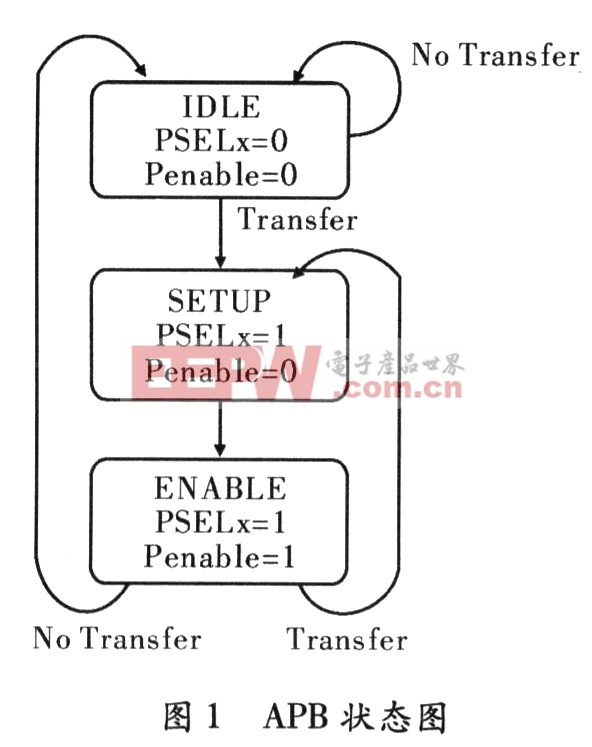

APB狀態機,如圖1所示。

APB這3個狀態描述如下:

IDLE:默認初始狀態。

Setup:當有一個傳輸請求,總線將進入Setup狀態,當PSELx,信號被選擇。總線只在Setup狀態停留一個周期,并將在時鐘的上升沿進入Enable狀態。

評論