dsp+fpga 文章 最新資訊

FPGA+DSP結(jié)構(gòu)嵌入式系統(tǒng)的FPGA配置方法及其實(shí)現(xiàn)

- 0 引言在信號處理領(lǐng)域中,基于FPGA+DSP的結(jié)構(gòu)設(shè)計(jì)已經(jīng)是系統(tǒng)發(fā)展的一個重要方向。隨著該系統(tǒng)設(shè)計(jì)的廣泛應(yīng)用,功能變得更加豐富,成本日趨低廉。而在某些小型化應(yīng)用的場合中,對系統(tǒng)體積的要求越來越高,因此如何在硬

- 關(guān)鍵字: FPGA DSP 嵌入式系統(tǒng) 配置方法

DSP應(yīng)用設(shè)計(jì)關(guān)鍵之接口設(shè)計(jì)(四)

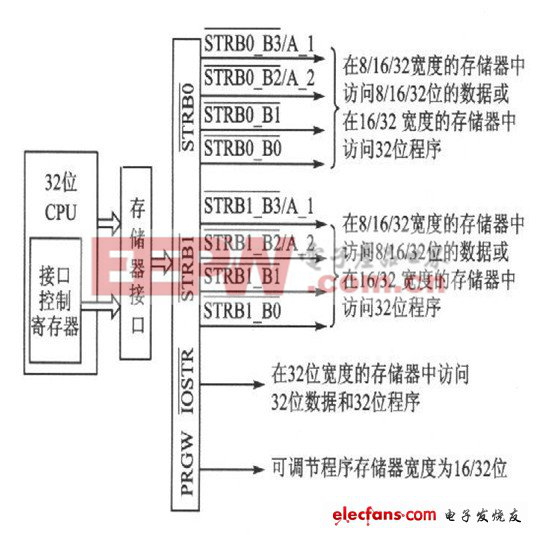

- DSP應(yīng)用設(shè)計(jì)關(guān)鍵之接口設(shè)計(jì)(四),四、TMS320C32的存儲器接口設(shè)計(jì) 1 TMS320C32的外部存儲器接口的特點(diǎn) TMS320C32是一個32位微處理器,它可以通過24位地址總線、32位數(shù)據(jù)總線和選通信號對外部存儲器進(jìn)行訪問。其外部存儲器接口結(jié)構(gòu)如下圖l所示。

- 關(guān)鍵字: 設(shè)計(jì) 接口 關(guān)鍵 DSP 應(yīng)用

DSP應(yīng)用設(shè)計(jì)關(guān)鍵之接口設(shè)計(jì)(三)

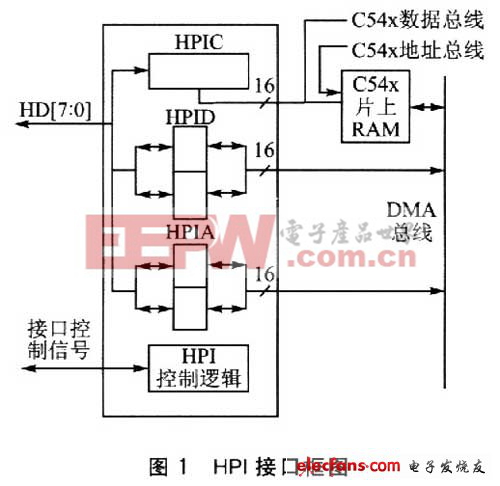

- DSP應(yīng)用設(shè)計(jì)關(guān)鍵之接口設(shè)計(jì)(三),三、PCI總線接口與DSP的HPI接口 1 HPI接口功能及特點(diǎn) 主機(jī)接口HPI(Host Pott Interface)是C54x DSP系列定點(diǎn)芯片內(nèi)部具有的一種并行接口部件,主要用于與其他總線或CPU之間進(jìn)行通信,其接口框圖如圖l所示。主機(jī)

- 關(guān)鍵字: 設(shè)計(jì) 接口 關(guān)鍵 DSP 應(yīng)用

DSP應(yīng)用設(shè)計(jì)關(guān)鍵之接口設(shè)計(jì)(二)

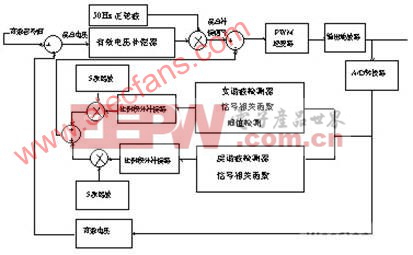

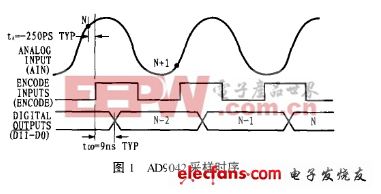

- DSP應(yīng)用設(shè)計(jì)關(guān)鍵之接口設(shè)計(jì)(二),二、FIFO實(shí)現(xiàn)高速模數(shù)轉(zhuǎn)換器與DSP的接口 在數(shù)字信號處理系統(tǒng)中,大多數(shù)高速模數(shù)轉(zhuǎn)換器都不能直接與DSP相連接。FIFO恰好架起了DSP與ADC之間的一座橋梁,因?yàn)樗芫彺娲罅康臄?shù)據(jù)塊。同時由于DSP訪問外部存儲器器件必

- 關(guān)鍵字: 設(shè)計(jì) 接口 關(guān)鍵 DSP 應(yīng)用

DSP應(yīng)用設(shè)計(jì)關(guān)鍵之接口設(shè)計(jì)(一)

- DSP應(yīng)用設(shè)計(jì)關(guān)鍵之接口設(shè)計(jì)(一),一、基于DSP的USB接口設(shè)計(jì) 1 引言 通過DSP 處理的數(shù)據(jù)往往要傳輸給PC 機(jī)進(jìn)行存儲和再處理,那么就必須解決DSP 與 PC 機(jī)之間的高速通信問題。本設(shè)計(jì)方案以德州儀器(TI)的C5000 系列DSP 芯片TMS320VC5416為微處理

- 關(guān)鍵字: 設(shè)計(jì) 接口 關(guān)鍵 DSP 應(yīng)用

用FPGA實(shí)現(xiàn)Nios II嵌入式系統(tǒng)配置技術(shù)

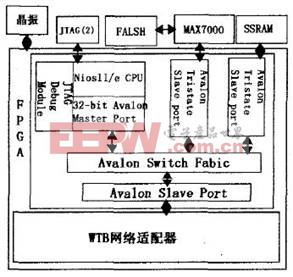

- 用FPGA實(shí)現(xiàn)Nios II嵌入式系統(tǒng)配置技術(shù),現(xiàn)場可編程門陣列(FPGA,F(xiàn)ield Programmable Gate Array)是一種高密度可編程邏輯器件,其邏輯功能是通過把設(shè)計(jì)生成的數(shù)據(jù)文件配置進(jìn)芯片內(nèi)部的靜態(tài)配置數(shù)據(jù)存儲器(SRAM )來實(shí)現(xiàn)的,具有可重復(fù)編程性,可以靈活實(shí)現(xiàn)各

- 關(guān)鍵字: 系統(tǒng) 配置 技術(shù) 嵌入式 II 實(shí)現(xiàn) Nios FPGA

交換位技術(shù)改進(jìn)FPGA-PWM計(jì)數(shù)器性能

- 簡單改變FPGA計(jì)數(shù)器規(guī)格使作為DAC功能PWM計(jì)數(shù)器的紋波降低。 當(dāng)需要一些模擬輸出和系統(tǒng)中有FPGA時,很可能選擇使用如圖1的PWM模塊和簡單低通濾波器。FPGA的輸出是固定頻率、計(jì)數(shù)器和數(shù)字比較器使占空比可變的典

- 關(guān)鍵字: FPGA-PWM 技術(shù)改進(jìn) 計(jì)數(shù)器 性能

基于DSP和CPLD增強(qiáng)數(shù)據(jù)采集的可擴(kuò)展性

- 電子產(chǎn)品世界,為電子工程師提供全面的電子產(chǎn)品信息和行業(yè)解決方案,是電子工程師的技術(shù)中心和交流中心,是電子產(chǎn)品的市場中心,EEPW 20年的品牌歷史,是電子工程師的網(wǎng)絡(luò)家園

- 關(guān)鍵字: DSP 數(shù)據(jù)采集 CPLD 可擴(kuò)展性

Altera全新Qsys工具加速FPGA產(chǎn)品上市步伐

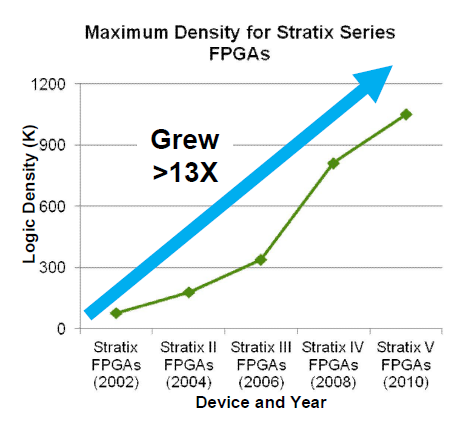

- 在FPGA設(shè)計(jì)領(lǐng)域目前存在著三大主要難題:設(shè)計(jì)規(guī)模擴(kuò)大、設(shè)計(jì)重用、設(shè)計(jì)驗(yàn)證時間太長。這三大難題嚴(yán)重影響著FPGA設(shè)計(jì)的效能,將減緩產(chǎn)品由研發(fā)到上市的時間,是亟需解決的重點(diǎn)問題。 2012年3月30日,“Altera亞太區(qū)采用Qsys實(shí)現(xiàn)系統(tǒng)集成研討會•北京站”在清華大學(xué)舉行,該活動重點(diǎn)介紹了Altera新的系統(tǒng)集成工具Qsys,及其如何通過Qsys提高設(shè)計(jì)效能。 簡化設(shè)計(jì)過程 隨著半導(dǎo)體技術(shù)的不斷發(fā)展,由于半導(dǎo)體工藝的不斷提升,器件的集成度也隨之提升

- 關(guān)鍵字: Altera FPGA Qsys

dsp+fpga介紹

您好,目前還沒有人創(chuàng)建詞條dsp+fpga!

歡迎您創(chuàng)建該詞條,闡述對dsp+fpga的理解,并與今后在此搜索dsp+fpga的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對dsp+fpga的理解,并與今后在此搜索dsp+fpga的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司