基于DSP的H.264編碼器的系統設計與優化

1 引言

本文引用地址:http://www.104case.com/article/257597.htmH.264是ITU-T的視頻編碼專家組(VCEG)和ISO/IEC的活動圖像專家組(MPEG)聯合制定的視頻壓縮標準。它在H.263/H.263++的基礎上發展,在繼承所有編碼壓縮技術優點的同時引入許多全新的編碼技術和網絡適配層NAL的概念,從而擁有更高的編碼效率和更好的網絡適配性。為從低碼率的實時通信系統或無線環境到高碼率的HDTV和數字存儲系統提供一個優良的視頻壓縮編碼通用工具。但H.264標準優異的性能表現是以編碼運算復雜度和運算量大為代價,在通用的PC機平臺實現會占用較大的CPU和內存資源。隨著數字信號處理器(DSP)技術的高速發展,DSP的處理速度和能力飛速提高。DSP已滿足H.264標準的編解碼運算速度要求。因此,在穩定的媒體處理器平臺上實現H.264標準有著較好的工程意義和應用前景。

詳細介紹了以TMS320DM6446DSP為核心的視頻編碼系統的硬件設計,并重點研究了H.264編碼器在以TMS320DM 6446為目標的CCS平臺上的移植和優化工作。

2 視頻編碼系統硬件設計

2.1 DSP的選型

DSP選用TI公司的Davinci媒體處理專用器件TMS320DM6446(簡稱DM6446)。它采用ARM+DSP雙核架構,包含一個TMS320C64x+核心和一個ARM926EJ-S核心。C64x+核心采用改進的超長指令字VLIW體系結構,內部擁有8個并行的運算單元,時鐘頻率600 MHz,峰值處理能力高達4 752 MI/s。DM6446片內為兩級高速緩存(Cache)結構,設計有獨立的32位DDR2 SDRAM接口和16位異步EMIF接口。此外,DM6446還集成有多種適用于視音頻多媒體處理的片內資源和接口,如用于和外部解碼器連接的視頻處理前端模塊VPFE、和視頻顯示設備連接的視頻處理后端模塊VPBE、多通道音頻串口等。

DM6446不僅在處理性能上完全滿足H.264標準要求。而且在內部結構、片內資源和外部接口上對視頻處理應用專門優化,大大降低視頻應用的開發難度和成本。

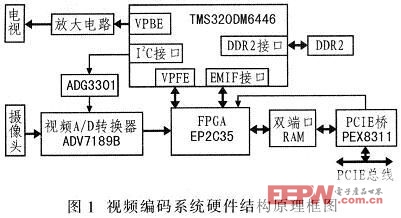

2.2 系統結構框圖

視頻編碼系統硬件結構原理框圖如圖1所示。主機通過PCIE總線對DSP進行初始化加載程序。攝像頭輸出的模擬視頻信號經視頻解碼模塊轉換為數字信號,經FPGA轉換電平。通過DM6446的VPFE模塊接口送人DSP,進行壓縮編碼處理。編碼后的視頻數據從DM6446的EMIF接口輸出通過PCIE總線送回主機進行下一步處理。DM6446的VPBE模塊可將采集的數字視頻信號再轉換為模擬信號輸出至電視進行監控。DDR2 SDRAM存儲編碼過程中的原始圖像、參考幀、編碼參數等數據。DM6446通過I2C總線配置A/D轉換器。FPGA與PCIE橋PEX8311之間加入雙端口RAM,以提高數據的傳輸效率。

2.3 視頻解碼模塊設計

模擬視頻信號的傳輸格式種類很多,而且國際上對數字視頻信號的傳輸格式有明確的標準規定,因此一般通用的A/D轉換器并不適合視頻領域應用。這里選用專用的視頻解碼器ADV7189B,它支持12路模擬視頻通道,包含3個具有防噪性能的12位54 MHz的A/D轉換器。支持CVBS、S-端子、YprPb 3種格式的模擬視頻信號輸入,能夠自動偵測NTSL/PAL/SECAM制式,輸出ITU-R BT.656標準的數字視頻信號。選用12路模擬通道中的3路,復用的支持3種模擬視頻格式。ADV7189B輸出10位數字視頻信號、獨立的垂直同步信號VD、水平同步信號HD和像素同步時鐘LLC1,電壓均為3.3 V電平,經過FPGA轉換為DM6446要求的1.8 V,然后從DM6446的VPFE模塊專用數字視頻信號接口送入DSP。壓縮編碼前,VPFE模塊將ITU-R BT.656標準的視頻數據轉換為H.264兼容的YUV4:2:O格式,存入DDR2 SDRAM中。VPFE模塊還支持對視頻數據進行白平衡、縮放等預處理操作。ADG3301實現I2C總線的電平轉換。

2.4 視頻編碼模塊設計

DM6446片內的VPBE模塊包含4個54 MHz的D/A轉換器,可在DM6446內部將數字視頻信號直接轉化為模擬視頻信號,4路輸出,并且支持CVBS、S-端子、YprPb 3種模擬視頻格式。因此,視頻編碼模塊設計較為簡單,只需對4路模擬輸出信號放大,就可直接與監視設備連接。選用TI公司的電壓反饋CMOS運算放大器OPA357進行運算放大。

評論