- CPLD(Complex programmable Logic Device,復雜可編程邏輯器件)是在傳統的PAL、GAL基礎上發展而來的,具有多種工作方式和高集成、高速、高可靠性等明顯的特點。

在超高速領域和實時測控方面有非常廣泛的應用,日前的CPLD普遍基于E2PROM和Flash電可擦除技術,可實現100次以上擦寫循環。

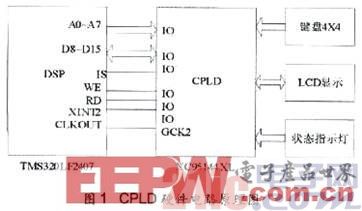

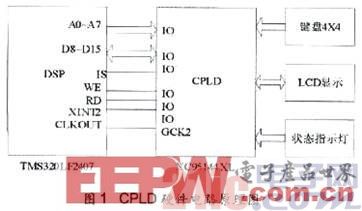

CPLD選擇及其擴展模塊的設計

由于A是3.3v電平供電的,所以CPLD我們也選擇3.3v電平供電的XL型號。XC95144XL是Xilinx公司 XC9500系列的一種。它

- 關鍵字:

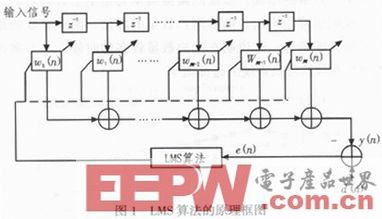

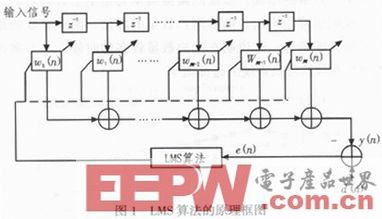

CPLD DSP

- 摘要:近年來,自適應均衡技術在通信系統中的應用日益廣泛,利用自適應均衡技術在多徑環境中可以有效地提高數字接收機的性能。為了適應寬帶數字接收機的高速率特點,本文闡述了自適應均衡器的原理并對其進行改進。最后使用FPGA芯片和Verilog HDL設計實現了自適應均衡器并仿真驗證了新方法的有效性。

信道均衡技術(Channel equalization)是指為了提高衰落信道中的通信系統的傳輸性能而采取的一種抗衰落措施。它主要是減小信道的多徑時延帶來的碼間串擾(ISI)問題。其原理是對信道或整個傳輸系統特性進行

- 關鍵字:

FPGA LMS

- 京微雅格的HR系列FPGA芯片已經能夠提供EVB,并預計今年第三季度大規模量產,已成為世界上除美國外唯一自主研發并成功量產FPGA產品的公司。

- 關鍵字:

京微雅格 FPGA

- 十四個月之前,我參加了一次Plunify的媒體沙龍活動,寫了一篇名為《云時代才剛剛開始》的文章,談了一點我對把芯片設計結合云計算和對Plunify這家創業公司的看法。那時候,Plunify主推的業務是租用亞馬遜的服務器資源,搭建一個FPGA開發的云端平臺,讓設計公司可以把設計方案上傳到云端來仿真,以節省大量的時間,同時也避開了自建云的昂貴成本。 一年過去了,我終于又有機會和Plunify做一次更加深入的交流,看看Plunify在中國大陸市場的深水里摸了一年石頭后,到底有沒有摸到魚。 Plunify

- 關鍵字:

Plunify 云端 FPGA InTime

- 時間都去哪了?當公司全球上下熱烈慶祝成立30周年的時候, 回首我在賽靈思竟然也已有十載。從上海到北京,從新天地到盤古大觀,從北京最開始幾個人的小辦事處到今天數十人數千規模的北京公司,我有幸見證了賽靈思在中國的巨大發展和變遷,但不變的是這份工作帶來的強大吸引力和提供給大家的實現夢想的舞臺。

賽靈思是我的第一份工作,一做就做了十年。很多周圍的同學朋友都已經換了多家公司,也有很多在高校都成了學術帶頭人,教授, 也不停地有獵頭和朋友追問我為什么不愿意動一動。 我清楚我的執著和堅守來源于公司人性化和平等的

- 關鍵字:

賽靈思 FPGA PAE

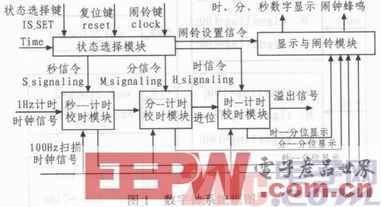

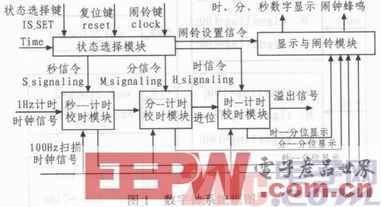

- 摘要:采用FPGA進行的數字電路設計具有更大的靈活性和通用性,已成為目前數字電路設計的主流方法之一。本文給出一種基于FPGA的數字鐘設計方案。該方案采用VHDL設計底層模塊,采用電路原理圖設計頂層系統。整個系統在QuartusⅡ開發平臺上完成設計、編譯和仿真,并在FPGA硬件實驗箱上進行測試。測試結果表明該設計方案切實可行。

EDA(Electronic Design Automation)又名電子設計自動化,其基本特征是:以超大規模可編程邏輯器件,如FPGA,為設計載體,以硬件描述語言,如VHDL,為

- 關鍵字:

FPGA QuartusⅡ

- 曾有句話這樣說到:“當你認為設計完美的時候,不是因為沒有什么可以加,而是你不能再去除什么。”這話用在FPGA上是再合適不過了。從簡單的邏輯集成到現在集成ARM核、DSP、模擬電路、存儲器等無所不包的系統級集成,從純硬件開發到可以用C、C++或System C來開發,從此前價格高昂到現在低成本低功耗,從工藝的跟隨到成為先進工藝的引領和3D IC的成功,從傳統的通信、工業和軍工等應用向消費電子、醫療電子、汽車電子、嵌入式市場等擴展,FPGA成為擴充我們想像力的“先鋒”。

- 關鍵字:

賽靈思 FPGA All Programmable

- 您有沒有留意到賽靈思的logo下面有兩個英文單詞——“All Programmable”? 這代表了什么?眾所周知,賽靈思一直是FPGA行業的領頭羊。那么未來呢?未來具有無限的可能性,但是All Programmable無疑是賽靈思正在全力推動的轉型。All Programmable SoC無疑是這個轉型的代表之作,Zynq這個革命性的產品,也就應運而生了。我和賽靈思的緣分也由此開始。

- 關鍵字:

賽靈思 FPGA Zynq

- 在FPGA領域,我們再次聞到了沉重的火藥味。2010年中國農歷新年前后,FPGA的28nm交響曲奏響。

- 關鍵字:

賽靈思 ASIC FPGA 28nm

- 寫這篇文章的時候,我正處于碩士研究生畢業論文的準備階段,眼睜睜看著我的大學生活即將畫上句號,再看看身邊有很多低年級的學生們一天天把時間白白荒費掉,我在心里替他們惋惜,在即將結束我的大學生活之際,我將我的大學幾年的有意義的生活與大家分享,看過這篇文章后也許能讓那些有夢想的同學為了實現自己的人生目標少走些彎路,大家要相信,大學校園——將為你提供一生最好的學習環境。

我高中畢業于新疆伊寧市三中,2002年考入哈爾濱工程大學信息與通信工程學院電子信息工程專業,2006年以創新人才

- 關鍵字:

DSP ARM FPGA/CPLD

- 規范很重要

工作過的朋友肯定知道,公司里是很強調規范的,特別是對于大的設計(無論軟件還是硬件),不按照規范走幾乎是不可實現的。邏輯設計也是這樣:如果不按規范做的話,過一個月后調試時發現有錯,回頭再看自己寫的代碼,估計很多信號功能都忘了,更不要說檢錯了;如果一個項目做了一半一個人走了,接班的估計得從頭開始設計;如果需要在原來的版本基礎上增加新功能,很可能也得從頭來過,很難做到設計的可重用性。

在邏輯方面,我覺得比較重要的規范有這些:

1.設計必須文檔化。要將設計思路,詳細實現等寫入文檔

- 關鍵字:

FPGA 時序 電路

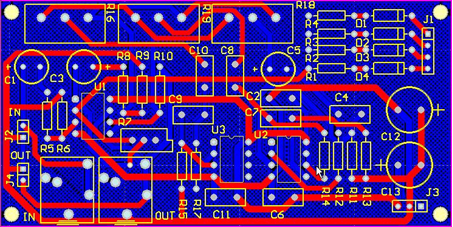

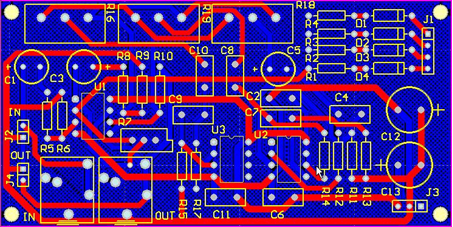

- 第一次做電路板是讀高中的時候,從每周20塊錢的生活費里省下一半來買元器件和材料。那樣糾結著做出了自己的第一塊電路板。敷銅板,透明膠帶,三氯化鐵,松香,焊條,現在想來還帶著那么一種讓人難以釋懷的親熱勁兒。原理一知半解的,照著書上的原理圖在敷銅板上畫出線,然后用透明膠帶裁成細條粘到需要保留的部分,再放到三氯化鐵溶液 里腐蝕。一晚上起來看好幾次,翻翻攪攪,最后一次醒來發現漂亮的小板已經腐蝕好了。然后焊接調試……

可惜第一次以失敗告終,板 子沒有調試成功。現在已經回憶不起當時

- 關鍵字:

元器件 DSP LED

- 今年是賽靈思公司成立30周年的日子,我衷心地對我們的公司說一聲“Happy Birthday”。我是2003年加入賽靈思的,今年也是我在賽靈思的第十一年。我在賽靈思的工作歷程也是賽靈思在中國的發展歷程,更是賽靈思支持中國自主知識產權創新的光輝歷程。

賽靈思的發言人在眾多場合無數次提到,我們致力于自主創新,并且能夠幫助實現中國“智”造。我個人的親身感受也確實如此。在我加入賽靈思的時候是從事FAE的工作,現在也還是在做技術相關的工作。很多客戶都知道,賽

- 關鍵字:

賽靈思 FPGA TD

- 摘要 文中對適用于高速突發通信的基于數字濾波平方的定時同步算法進行了研究。通過對在高速數據傳輸通信中,該定時同步環路的定時誤差估計模塊進行并行結構實現,大幅降低了系統對于時鐘的要求,且更加易于實現;將文中所提定時控制部分與其他文獻中的方法做了對比,表明所用方法可以達到更好的效果。最后進行的Matlab仿真以及硬件實現,結果表明,該環路可以實現突發與非突發情況下的高速數傳定時同步。

目前,數字通信系統正向高速全數字化方向發展。在全數字接收機定時同步中,主要包括兩個關鍵點:定時誤差估計和定時控制。傳統的定時

- 關鍵字:

FPGA Matlab

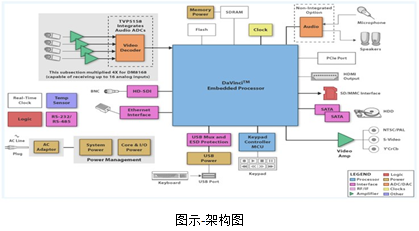

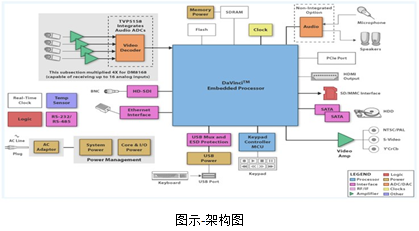

- 2014年5月15日,致力于亞太地區市場的領先電子元器件分銷商---大聯大控股宣布,其旗下友尚推出基于TI達芬奇系列DSP的DVR方案。

TI的達芬奇(DaVinciTM )技術是一組專門為高效和引人注目的數字視頻而設計的基于 DSP 的系統解決方案 – 適用于數碼攝像機、視頻安全設備、高級醫療成像設備、便攜式視頻播放器或其他視頻應用。這種系統針對靈活的數字視頻實施而進行了精心優化,擁有業界領先的性能并集成了可編程數字信號處理器(DSP)內核、ARM處理器以及視頻加速協處理器。憑借高

- 關鍵字:

大聯大 DSP DVR

dsp+fpga介紹

您好,目前還沒有人創建詞條dsp+fpga!

歡迎您創建該詞條,闡述對dsp+fpga的理解,并與今后在此搜索dsp+fpga的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473