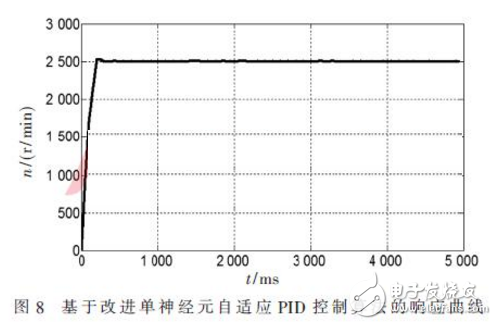

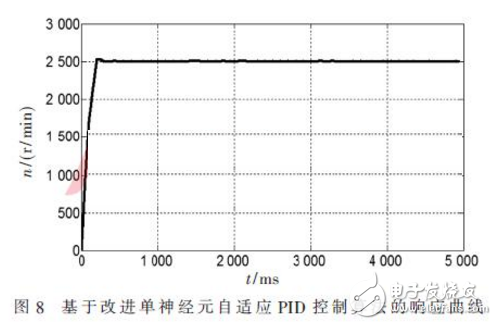

- 基于DSP的三相8極無刷直流電機控制設計-本文給出了基于TMS320F28335 DSP的無刷直流電機的控制系統設計方案,對控制系統的主要硬件電路模塊進行了詳細設計,包括電機驅動電路和控制電路的設計。并給出了轉速調節子程序的設計方法。

- 關鍵字:

DSP TMS32 電機控制 直流電機 BLDC

- 通過FPGA智能調試工具縮短驗證時間-設計人員選擇具有優秀調試能力的FPGA器件,可以縮短開發周期并降低成本,同時顯著加快上市速度。

- 關鍵字:

FPGA 邏輯分析儀

- 基于FPGA的虛擬現實定位系統-虛擬現實技術是目前計算機信息科學中的前沿學科,文中設計了一種以FPGA 為核心的數據采集處理系統.利用HMC5883L和ADXL345對虛擬場景中物體的方位和朝向進行確定并通過以太網給虛擬場景主機發送數據.整個系統以 FPGA作為主控制器,配以傳感器數據采集,內部FIFO存儲,以太網高速傳輸,從而把定位系統參數實時傳送到上位機中,具有傳輸速度快.實時性等優點,實現了虛擬現實高精度定位的功能.

- 關鍵字:

FPGA 虛擬現實

- 電路設計常見的八個誤區-電路設計常見的八個誤區:現象一:這板子的PCB設計要求不高,就用細一點的線,自動布吧;現象二:這些總線信號都用電阻拉一下,感覺放心些;現象三:CPU和FPGA的這些不用的I/O口怎么處理呢?先讓它空著吧,以后再說。

- 關鍵字:

電路設計 PCB fpga

- FPGA實戰開發技巧(6)-時序性能是FPGA 設計最重要的指標之一。造成時序性能差的根本原因有很多,但其直接原因可分為三類:布局較差、邏輯級數過多以及信號扇出過高。

- 關鍵字:

FPGA 時序性能

- FPGA實戰開發技巧(7)-通常我們會為工程添加UCF 約束指定時序要求和管腳約束。但是UCF 約束是給MAP,PAR 等實現使用的,綜合工具XST 并不能感知系統的時序要求。而為XST 添加XCF 約束卻是使實現結果擁有最高頻率的關鍵。

- 關鍵字:

FPGA XCF UCF

- 利用FPGA的自身特性實現隨機數發生器-本文主要介紹利用FPGA的自身的特性實現隨機數發生器,在Virtex-II Pro開發板上用ChipScope觀察隨機數序列,以及在PCIe4Base(基于Virtex-4 FPGA)上實現。

- 關鍵字:

fpga

- 談談如何利用FPGA開發板進行ASIC原型開發-ASIC設計在尺寸和復雜性上不斷增加,現代FPGA的容量和性能的新進展意味著這些設計中的2/3能夠使用單個FPGA進行建模。

- 關鍵字:

FPGA ASIC

- FPGA實戰開發技巧(5)-一般來講,添加約束的原則為先附加全局約束,再補充局部約束,而且局部約束比較寬松。其目的是在可能的地方盡量放松約束,提高布線成功概率,減少ISE 布局布線時間。典型的全局約束包括周期約束和偏移約束。

- 關鍵字:

FPGA 周期約束

- FPGA實戰開發技巧(4)-在代碼編寫完畢后,需要借助于測試平臺來驗證所設計的模塊是否滿足要求。ISE 提供了兩種測試平臺的建立方法,一種是使用HDL Bencher 的圖形化波形編輯功能編寫,另一種就是利用HDL 語言,相對于前者使用簡單、功能強大。

- 關鍵字:

FPGA ISE

- FPGA實戰開發技巧(3)-所謂綜合,就是將HDL語言、原理圖等設計輸入翻譯成由與、或、非門和RAM、觸發器等基本邏輯單元的邏輯連接( 網表),并根據目標和要求( 約束條件) 優化所生成的邏輯連接,生成EDF 文件。XST 內嵌在ISE 3 以后的版本中,并且在不斷完善。

- 關鍵字:

FPGA 賽靈思

- FPGA電路必須遵循的原則和技巧-在調試FPGA電路時要遵循必須的原則和技巧,才能降低調試時間,防止誤操作損壞電路。通常情況下,能夠參考以下步驟執行 FPGA硬件系統的調試。

- 關鍵字:

FPGA

- 寫verilog代碼要有硬件的概念-因為Verilog是一種硬件描述語言,所以在寫Verilog語言時,首先要有所要寫的module在硬件上如何實現的概念,而不是去想編譯器如何去解釋這個module

- 關鍵字:

verilog FPGA

- 學好FPGA應該要具備的知識-閱讀本文的人群:熟悉數字電路基本知識(如加法器、計數器、RAM等),熟悉基本的同步電路設計方法,熟悉HDL語言,對FPGA的結構有所了解,對FPGA設計流程比較了解。

- 關鍵字:

FPGA 同步電路

- 解密業界首款16nm產品核心技術-以賽靈思 20nm UltraScale 系列的成功為基礎,賽靈思現又推出了全新的 16nm UltraScale+ 系列 FPGA、3D IC 和 MPSoC,憑借新型存儲器、3D-on-3D 和多處理SoC(MPSoC)技術,再次領先一代提供了遙遙領先的價值優勢。

- 關鍵字:

賽靈思 FPGA 16nm制程

dsp+fpga介紹

您好,目前還沒有人創建詞條dsp+fpga!

歡迎您創建該詞條,闡述對dsp+fpga的理解,并與今后在此搜索dsp+fpga的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473