FPGA實戰(zhàn)開發(fā)技巧(12)

5.6 大規(guī)模設(shè)計的調(diào)試經(jīng)驗

在大規(guī)模設(shè)計的調(diào)試應(yīng)該按照和設(shè)計理念相反的順序,從底層測試,主要依靠ChipScope Pro 工具。下面主要介紹ChipScope Pro、FPGA Editor 組件的使用方法。

本文引用地址:http://www.104case.com/article/201710/365625.htm5.6.1 ChipScope Pro組件應(yīng)用實例

在賽靈思軟件設(shè)計工具中,ISE 可集成賽靈思公司的所有工具和程序。ChipScope Pro 也不例外,在ISE 中將其作為一類源文件,和HDL 源文件、IP Core 以及嵌入式系統(tǒng)的地位是等同的。本節(jié)在Xilinx Spartan3E-D開發(fā)板上實現(xiàn)一個計數(shù)器模塊,基于該模塊詳細(xì)介紹如何在ISE 中新建ChipScope 應(yīng)用以及觀察、分析數(shù)據(jù)的詳細(xì)操作。

例5.6.1 :在ISE 中實現(xiàn)一個8 比特計數(shù)器,利用ChipScope 分析其邏輯輸出。

(1) 新建用戶工程,添加mycounter.v 的源文件,其內(nèi)容如下所列:

module mycounter(clk, reset, dout);

input clk;

input reset;

output [7:0] dout;

reg [7:0] dout;

always @(posedge clk) begin

if (reset == 0)

dout = 0;

else

dout = dout + 1;

end

endmodule

然后根據(jù)電路連接,添加相應(yīng)的管腳約束。

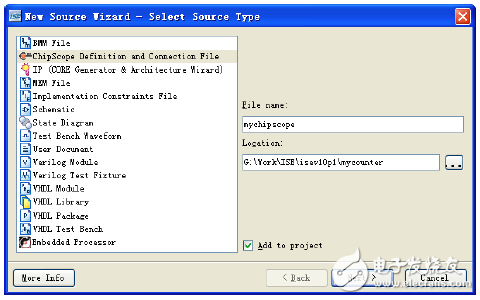

(2) 綜合工程,然后在ISE 工程管理區(qū),單擊右鍵,選擇“Add New Source”命令,在彈出的對話框中選擇“ChipScope DefiniTIon and ConnecTIon File” 類型, 并在“File Name” 欄輸入ChipScope 設(shè)計名稱mychipscope,如圖5-41所示。

圖5-41 添加ChipScope設(shè)計示意圖

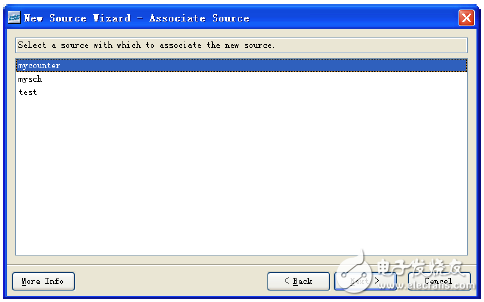

圖5-42 測試模塊選擇界面

單擊“Next”按鍵,進(jìn)入分析文件選擇界面,這里會將該文件夾里所有的HDL 設(shè)計、原理圖設(shè)計都羅列出來( 包括頂層模塊和全部底層模塊),供用戶挑選,用鼠標(biāo)單擊即可選中,本例選擇mycounter,如圖5-42 所示。單擊“Next”按鍵進(jìn)入小結(jié)頁面,單擊“Finish”按鍵完成添加。

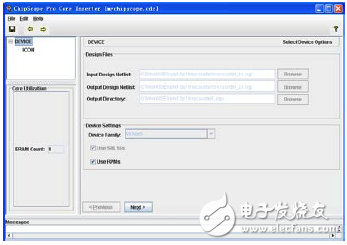

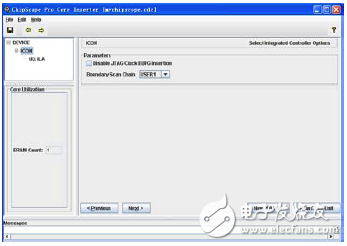

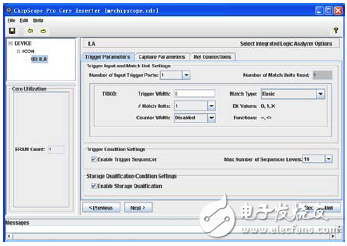

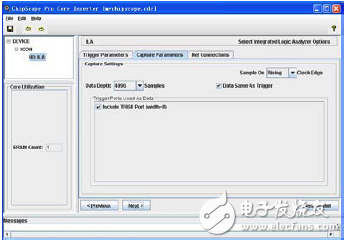

(3) 雙擊工程區(qū)mycounter.v 下的子模塊mychipscope.cdc,可自動打開Chipscope Pro Core Insterser軟件,添加觸發(fā)單元和觸發(fā)位寬。其中觸發(fā)類型選為Basic,位寬為8比特;設(shè)置采樣深度為4096,各步驟如圖5-43到圖5-46所示。

圖5-43 調(diào)試工程配置界面

圖5-44 ICON核配置界面

圖5-45 觸發(fā)信號配置界面

圖5-46 采集深度配置界面

(4) 點擊“Next”進(jìn)入網(wǎng)表連接顯示頁面,如圖5-47 所示。其中如果用戶定義的觸發(fā)和時鐘信號線有未連接的情況,則圖中“UNIT”、“CLOCKPORT”以及“TRIGGERPORTS”等字樣以紅色顯示;正確完成連接后則變成黑色。

圖5-47網(wǎng)表連接提示界面

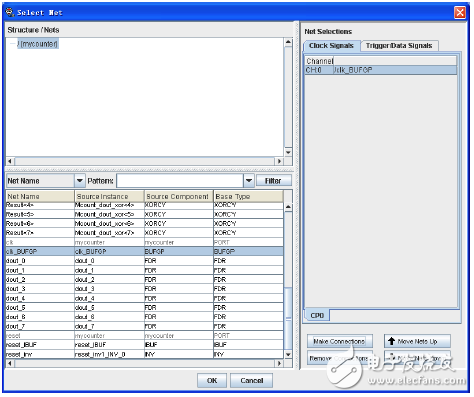

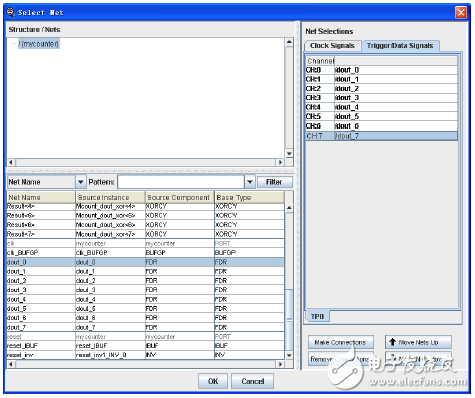

點擊圖5-47 中“Modify ConnecTIon”的按鍵,進(jìn)入連接頁面,時鐘和數(shù)據(jù)的連接如圖5-48、圖5-49所示。需要注意的是,ChipScope Pro 只能分析FPGA 設(shè)計的內(nèi)部信號,因此不能直接連接輸入信號的網(wǎng)表,所以輸入信號網(wǎng)表全部以灰色顯示。如果要采樣輸入信號,可通過連接其輸入緩沖信號來實現(xiàn),時鐘信號選擇相應(yīng)的BUFGP,普通信號選擇相應(yīng)的IBUF。如圖5-48 中所示,選擇采樣時鐘時,選擇了CLK_BUFGP。

圖5-48 時鐘網(wǎng)表連接界面

圖5-49 觸發(fā)網(wǎng)表連接界面

連接完成后,單擊“OK”按鍵返回連接顯示界面,發(fā)現(xiàn)所有提示字符“UNIT”、“CLOCKPORT”以及“TRIGGERPORTS”沒有紅色,則單擊“Return Project Navigator”,退出Chipscope,返回到ISE 中。否則需要再次點擊“Modify ConnecTIon”按鍵重新連接。

(5) 在工程中加入UCF 文件,約束時鐘、數(shù)據(jù)管腳位置。為了簡化也可以只添加clk 和reset 這兩個控制信號的管腳約束,其內(nèi)容如下:

NET clk LOC = C9 | IOSTANDARD = LVCMOS33 ;

# Define clock period for 50 MHz oscillator (40%/60% duty-cycle)

NET clk PERIOD = 20.0ns HIGH 40%;

NET reset LOC = H13 | IOSTANDARD = LVTTL | PULLDOWN ;

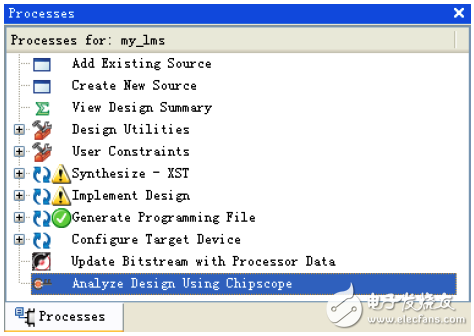

(6) 在ISE 過程控制區(qū)中雙擊“Implement Design”和“Generate Programming File”, 可以完成實現(xiàn)以及生成可編程文件,并將設(shè)計人員插入的各類核也將被包含在比特文件中。生成配置文件后,雙擊圖5-50所示的“Analyze Design Using Chipscope”圖標(biāo),可自動打開Chipscope Pro Analyzer 軟件。

圖5-50 Chipscope Pro Analyzer啟動操作示意圖

(7) 在Chipscope Analyzer 用戶界面上點擊工具欄上圖標(biāo)“ ”,初始化邊界掃描鏈。等掃描完成后,單擊“Device”菜單下“DEV: 0 My Device0(XC3S500E) → Configure”命令選擇.bit 文件配置FPGA。

(8) 芯片配置完成后,選擇“File”菜單的“Import”命令,可彈出CDC 文件加載頁面,選擇相應(yīng)的CDC 文件,將會把所有以“Dataport”的名稱修改為綜合后的線網(wǎng)名稱。

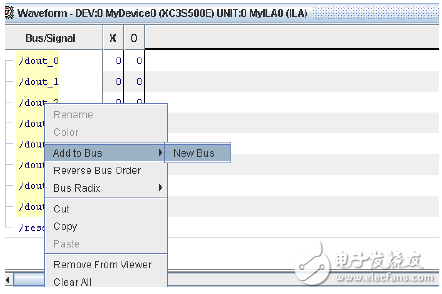

(9) 組合cnt 總線信號。可按住“Ctrl”鍵,選擇多個總線信號,單擊右鍵,選擇“Add to Bus”命令,將其組合成相應(yīng)的總線信號,如圖5-51 所示。

圖5-51 添加總線操作示意圖

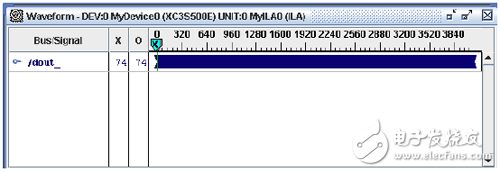

(10) 不設(shè)定觸發(fā)條件采集數(shù)據(jù)。點擊工具欄的“ ”圖標(biāo),開始采集數(shù)據(jù)。整體結(jié)果如圖5-52 所示,單擊工具欄的“ ”按鍵,可放大信號,局部結(jié)果如圖5-53 所示。從分析結(jié)果可以看出,本設(shè)計在FPGA中成功地完成了8 比特計數(shù)器的功能。

圖5-52 Analyzer分析結(jié)果整體示意圖

(11) 設(shè)定觸發(fā)條件采集數(shù)據(jù)。在“Trigger Setup”欄Match 區(qū)域的“M0: Trigger Port0”行的Value 列輸入觸發(fā)條件“0000_0000”,如圖5-54 所示。

點擊工具欄的“ ”圖標(biāo),開始采集數(shù)據(jù),可以看到,采集結(jié)果的第一個數(shù)為0,如圖5-55 所示。當(dāng)然,

用戶可以根據(jù)需要設(shè)置更復(fù)雜的觸發(fā)條件。

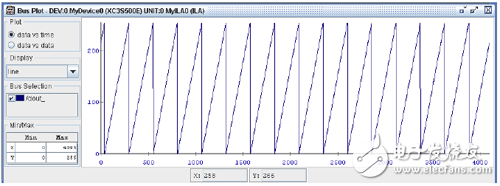

(12) 利用Bus Plot 功能繪制輸出信號波形。在工程區(qū)雙擊“Bus Plot”命令,然后在彈出窗口的“Bus Selection”區(qū)域選中“dout”,則會將采集數(shù)據(jù)以圖形方式顯示出來,如圖5-56 所示。由于本設(shè)計是8 比特加1 計數(shù)器,因此其波形就是幅度為0 到255 的鋸齒波。

圖5-56 8計數(shù)器的波形示意圖

評論