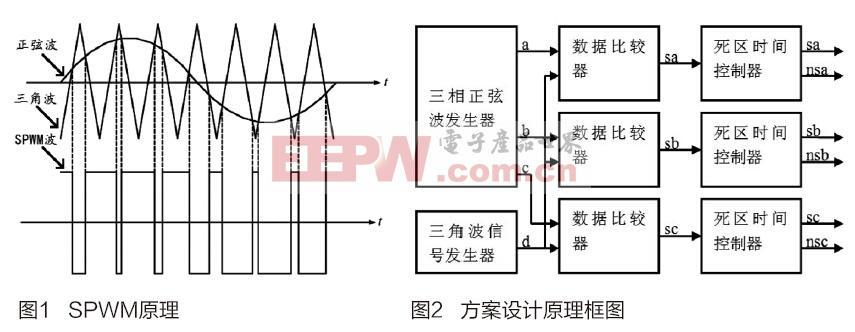

隨著在雷達探測、儀表測量、化學分析等領域研究的不斷深入,不僅要求定性的完成目標檢測,更加需要往高精度、高分辨率成像的方向發展。一方面,產生頻率、 幅度靈活可控,尤其是低相位噪聲、低雜散的頻率源對許多儀器設備起著關鍵作用。另一方面,電子元器件實際性能參數并非理想以及來存在自外部內部的干擾,大 量的誤差因素會嚴重影響系統的準確性。雙路參數可調的信號源可有效地對系統誤差、信號通道間不平衡進行較調,并且可以產生嚴格正交或相關的信號,這在弱信 號檢測中發揮重要作用。為此本文采用雙通道DDS方法,以STM32為控

關鍵字:

STM32 DDS

1引言

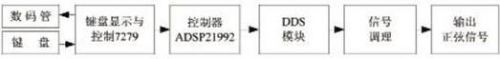

DDS同DSP(數字信號處理)一樣,是一項關鍵的數字化技術。DDS是直接數字式頻率合成器(DirectDigitalSynthesizer)的英文縮寫。與傳統的頻率合成器相比,DDS具有低成本、低功耗、高分辨率和快速轉換時間等優點,廣泛使用在電信與電子儀器領域,是實現設備全數字化的一個關鍵技術。在各行各業的測試應用中,信號源扮演著極為重要的作用。但信號源具有許多不同的類型,不同類型的信號源在功能和特性上各不相同,分別適用于許多不同的應用。目前,最常見的信號源類型包括任意波形發生器,函數發

關鍵字:

FPGA DDS

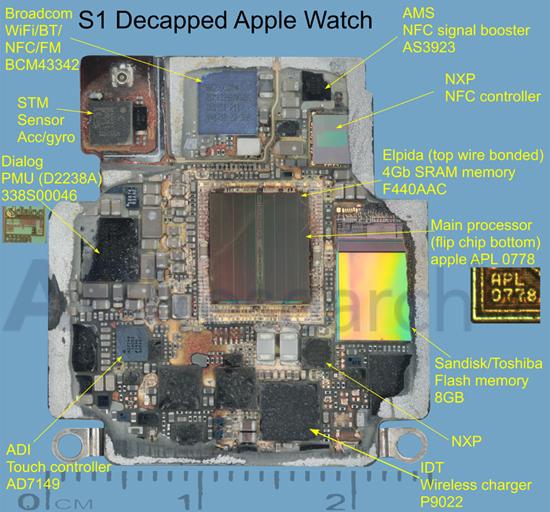

熱門的電子產品除了煎、炸、烹、炒、攪拌、挨槍子兒之外,免不了要到iFixit的螺絲刀下走一遍。蘋果的Apple Watch自然也逃脫不了,前兩天就已經被大卸八塊兒了。

在iFixit的螺絲刀、撬棒觸及不到的地方,比如Apple Watch嚴密封裝起來的S1芯片就需要能夠庖丁解牛的手術刀了。這一次ABI Research對S1進行了完全徹底的解剖,并辨識出了其中一些主要的部件。

從ABI提供的拆解照片可以清晰地看到Apple Watch的主板,中間是一個代號為APL 0778的芯片,這應該是

關鍵字:

Apple Watch S1

現代雷達面臨著綜合性電子干擾、反輻射導彈、低空和超低空突防以及目標隱身技術的等4大威脅,這就要求現代雷達具有反地物、抗積極和消極干擾、反隱身和自身生存的能力,其信號具有頻率捷變、波形參數捷變以及自適應跳頻的能力。因此對雷達信號產生器提出了越來越高的要求,要求具有寬頻帶、高精度、高穩定以及快速跳變的能力。隨著現代電子技術的發展,高性能直接數字合成DDS(Direct DigitalSynthesis)技術、數字信號處理DSP(Digital Signal Processing)技術及大規模可編程邏輯器件

關鍵字:

AD9858 DDS

0 引言

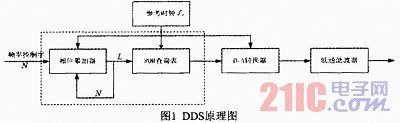

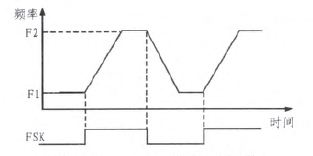

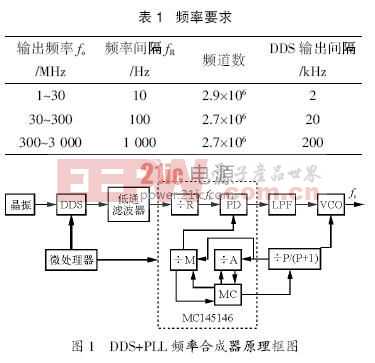

跳頻通信具有較強的抗干擾、抗多徑衰落、抗截獲等能力,已廣泛應用于軍事、交通、商業等各個領域。頻率合成器是跳頻系統的心臟,直接影響到跳頻信號的穩定性和產生頻率的準確度。目前頻率合成主要有三種方法:直接模擬合成法、鎖相環合成法和直接數字合成法(DDS)。直接模擬合成法利用倍頻(乘法)、分頻(除法)、混頻(加法與減法)及濾波,從單一或幾個參考頻率中產生多個所需的頻率。該方法頻率轉換時間快(小于100ns),但是體積大、功耗高,目前已基本不用。鎖相環合成法通過鎖相環完成頻率的加、減、乘、除運算

關鍵字:

DDS FPGA

高頻信號源設計是三維感應測井的重要組成部分。三維感應測井的原理是利用激勵信號源通過三個正交的發射線圈向外發射高頻信號,再通過多組三個正交的接收線圈,得到多組磁場分量,從而準確測量地層各向異性電阻率。在測井過程中,要求信號源的頻率為高頻,并且要求信號的頻率有很高的穩定性。

產生信號的方法很多,可以采用函數發生器外接分立元件來實現,通過調節外接電容或電阻來設置輸出信號頻率。但輸出信號受外部分立器件參數影響很大,且輸出信號頻率不能太高,同時無法實現頻率步進調節。另外,采用FPGA可實現信號發生器的設計

關鍵字:

DSP DDS

SOPC(System on a Programmable Chip,片上可編程系統)是Altera公司提出的一種靈活、高效的SOC解決方案。它將處理器、存儲器、I/O接口、LVDS、CDR等系統設計需要的功能模塊集成到一個可編程邏輯器件上,構建一個可編程的片上系統。它具有靈活的設計方式,軟硬件可裁減、可擴充、可升級,并具備軟硬件在系統可編程的功能。SOPC的核心器件FPGA已經發展成一種實用技術,讓系統設計者把開發新產品的時間和風險降到最小。最重要的是,具有現場可編程性的FPGA延長了產品在市場的存

關鍵字:

SOPC DDS Nios II Altera

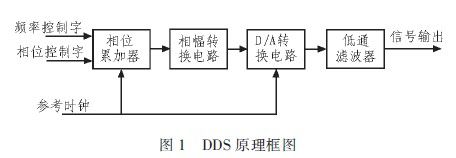

本文提出了一種采用VHDL硬件描述語言設計新型三相正弦脈寬調制(SPWM)波形發生器的方法。該方法以直接數字頻率合成技術(DDS)為核心產生三相SPWM信號。并且利用VHDL設計了死區時間可調的死區時間控制器,解決了傳統的模塊電路等待方法很難產生帶精確死區時間控制的SPWM信號的問題。該方法在Quartus II 9.1環境平臺下進行了仿真驗證,并將設計程序下載到DE2-70實驗板進行實驗測試,用示波器測試得到了死區時間可控制的SPWM波形。

關鍵字:

VHDL SPWM DDS 死區時間 FPGA 201505

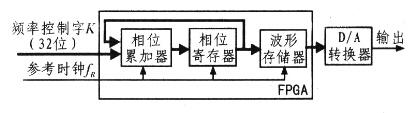

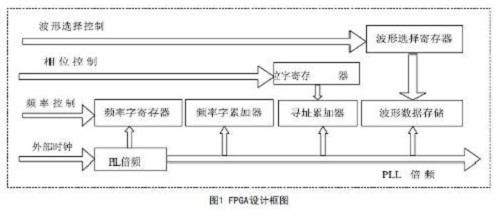

信號發生器是一種常用的信號源,廣泛應用于通信、測量、科研等現代電子技術領域。信號發生器的核心技術是頻率合成技術,主要方法有:直接模擬頻率合成、鎖相環頻率合成(PLL)、直接數字合成技術(DDS)。DDS 是開環系統,無反饋環節,輸出響應速度快,頻率穩定度高。因此直接數字頻率合成技術是目前頻率合成的主要技術之一。文中的主要內容是采用FPGA 結合虛擬儀器技術,進行DDS 信號發生器的開發[1-2]。

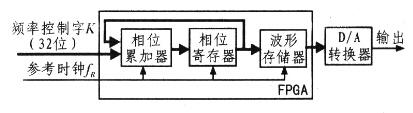

1 DDS 工作原理

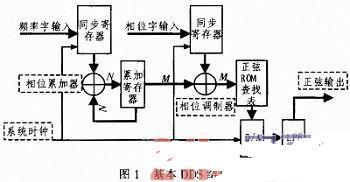

圖1 是DDS 基本結構框圖。以正弦波信號發生器為例,利用DDS 技術

關鍵字:

FPGA DDS

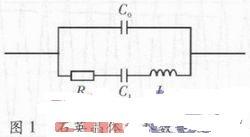

針對π網絡石英晶體參數測試系統,采用以STM32F103ZET6型ARM為MCU控制DDS產生激勵信號。該測試系統相對于傳統的PC機測試系統具有設備簡單、操作方便,較之普通單片機測試系統又具有資源豐富、運算速度更快等優點。AD9852型DDS在ARM控制下能產生0~100 MHz掃頻信號,經試驗數據分析得到信號精度達到0.5×10-6,基本滿足設計要求。該系統將以其小巧、快速、操作方便、等優點被廣泛采用。

產生正弦激勵信號一般可以通過振蕩電路或直接數字頻率合成器(Direct

關鍵字:

石英晶體 DDS

1.引言

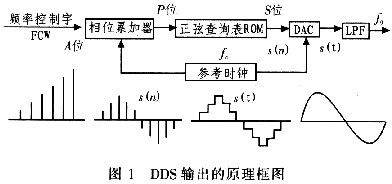

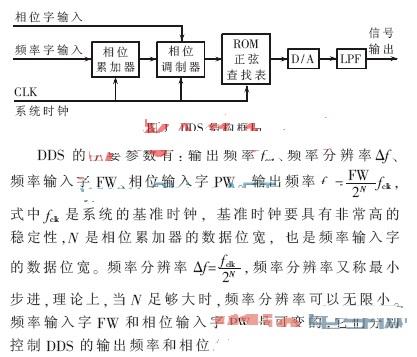

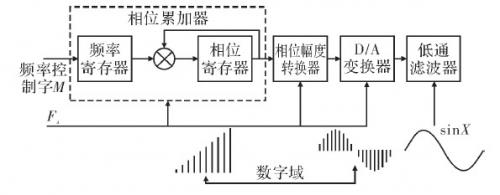

DDS頻率合成器具有頻率分辨率高,輸出頻點多,可達2N個頻點(假設DDS相位累加器的字長是N);頻率切換速度快,可達us量級;頻率切換時相位連續的優點,可以輸出寬帶正交信號,其輸出相位噪聲低,對參考頻率源的相位噪聲有改善作用;可以產生任意波形;全數字化實現,便于集成,體積小,重量輕。

本文介紹了DDS的基本原理,同時針對DDS波形發生器的FPGA實現進行了簡要介紹,利用SignalTapII嵌入式邏輯分析儀對正弦波、三角波、方波、鋸齒波進行仿真驗證。

2.DDS波形發生器的

關鍵字:

DDS 波形發生器

1971年,美國學者TIERNCY J、TADER C M和GOLD B在《A Digital Frequeney Synthesizer》一文中提出了以全數字技術,從相位概念出發直接合成所需波形的一種新的頻率合成原理,稱之為直接數字頻率合成器DDS(Direct Digitial Frequency Synthesis)[1].這是頻率合成技術的一次重大革命,但限于當時微電子技術和數字信號處理技術的限制,DDS并沒有得到足夠的重視。隨著現代超大規模集成電路集成工藝的高速發展,數字頻率合成技術得到了質

關鍵字:

FPGA DDS

文中介紹的干擾器能夠產生3種干擾信號:隨機干擾、點頻干擾和掃頻干擾,其中點頻干擾和掃頻干擾是基于單片機對DDS芯片AD9852的控制產生,整個系統的控制靈活、高效。測試結果表明,系統能夠準確產生所需要的干擾信號,滿足抗干擾性能測試的需要。雖然本設計產生的干擾信號位于406 MHz頻段,但這樣的電路結構也可用于其它頻段(需修改VCO、PLL等電路),例如手機通信頻段,因此本電路結構對其它頻段的應用同樣具有借鑒意義。

隨著電子設備的使用越來越普遍,電子設備之間的干擾問題也越來越突出,特別是通信設備的

關鍵字:

DDS AD9852

介紹了直接數字頻率合成(DDS)的結構和原理,并將DDS技術應用于短波射頻通信頻率源中。實現了一種基于單片機+DDS可編程低噪聲頻率源,輸出信號范圍46.5~75 MHz.實驗結果表明,該頻率源具有頻率分辨率高、相位噪聲低等優點,滿足短波射頻通信系統對頻率源的設計要求。

頻率源是現代短波射頻通信系統的核心,對整個系統的正常運行起著決定性的作用。作為射頻電路與系統的核心設備,頻率源的好壞關系著整個系統的穩定性。現在的頻率合成技術正朝著雜散和相位噪聲更低的方向發展,同時還要求有更寬的頻帶和更高的頻率

關鍵字:

DDS 射頻

摘要:基于零中頻正交解調原理的頻率特性測試儀,用于檢測被測網絡的幅頻特性和相頻特性。系統采用集成數字直接頻率合成器AD9854產生雙路恒幅正交余弦信號,作為掃頻信號源,以FPGA為控制核心和運算平臺,結合濾波器、放大器、混頻器及ADC電路,實現對雙端口網絡在1-40MHz頻率范圍內頻率特性的點頻和掃頻測量,并在LCD屏上實時顯示相頻特性曲線和幅頻特性曲線。

引言

AD9854數字合成器是高度集成的器件,它采用先進的DDS技術,片內整合了兩路高速、高性能正交D/A轉換器,在高穩定度時鐘的驅動

關鍵字:

AD9854 FPGA 濾波器 DDS ADC 201504

dds-s1介紹

您好,目前還沒有人創建詞條dds-s1!

歡迎您創建該詞條,闡述對dds-s1的理解,并與今后在此搜索dds-s1的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473