基于DDS技術(shù)的波形發(fā)生器設(shè)計(jì)與仿真

1.引言

本文引用地址:http://www.104case.com/article/272868.htmDDS頻率合成器具有頻率分辨率高,輸出頻點(diǎn)多,可達(dá)2N個(gè)頻點(diǎn)(假設(shè)DDS相位累加器的字長(zhǎng)是N);頻率切換速度快,可達(dá)us量級(jí);頻率切換時(shí)相位連續(xù)的優(yōu)點(diǎn),可以輸出寬帶正交信號(hào),其輸出相位噪聲低,對(duì)參考頻率源的相位噪聲有改善作用;可以產(chǎn)生任意波形;全數(shù)字化實(shí)現(xiàn),便于集成,體積小,重量輕。

本文介紹了DDS的基本原理,同時(shí)針對(duì)DDS波形發(fā)生器的FPGA實(shí)現(xiàn)進(jìn)行了簡(jiǎn)要介紹,利用SignalTapII嵌入式邏輯分析儀對(duì)正弦波、三角波、方波、鋸齒波進(jìn)行仿真驗(yàn)證。

2.DDS波形發(fā)生器的FPGA實(shí)現(xiàn)

FPGA的應(yīng)用不僅使得數(shù)字電路系統(tǒng)的設(shè)計(jì)非常方便,而且它的時(shí)鐘頻率已可達(dá)到幾百兆赫茲,加上它的靈活性和高可靠性,非常適合用于實(shí)現(xiàn)波形發(fā)生器的數(shù)字電路部分。使用FPGA設(shè)計(jì)DDS電路比采用專用DDS芯片更為靈活,只需改變FPGA中的ROM數(shù)據(jù),DDS就可以產(chǎn)生任意波形,具有相當(dāng)大的靈活性。

2.1 FPGA設(shè)計(jì)流程

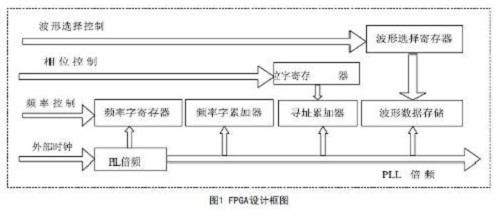

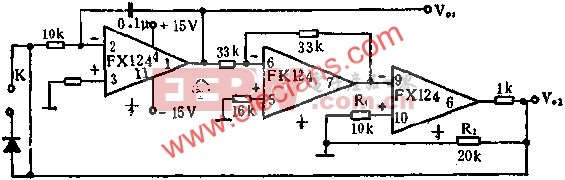

FPGA的設(shè)計(jì)框圖如圖1所示,F(xiàn)PGA的主要功能是:產(chǎn)生與外圍電路的接口電路,使其能夠接受外圍邏輯控制信號(hào);保存頻率字,并構(gòu)成相位累加器,產(chǎn)生與主時(shí)鐘相同頻率的RAM尋址字;用內(nèi)部的存儲(chǔ)塊構(gòu)成存放多種波形數(shù)據(jù)的ROM,并通過(guò)相應(yīng)的控制線進(jìn)行選擇;構(gòu)造出兩個(gè)多波形選擇輸出的輸出通道,其中的一路通道可具備移相功能;用內(nèi)部的PLL倍頻外部低頻晶振,并輸出與主時(shí)鐘同頻的時(shí)鐘,驅(qū)動(dòng)片外高速D/A.

2.2 時(shí)鐘模塊

根據(jù)耐奎斯特采樣定理要得到輸出頻率為10MHz的信號(hào),其所輸入的信號(hào)時(shí)鐘頻率必須達(dá)20MHz以上。采樣頻率越高,輸出波形的平坦度越好,同時(shí)波形的的采樣點(diǎn)數(shù)也越多,那么獲得的波形質(zhì)量也就越好。本設(shè)計(jì)中的DDS模塊是一高速模塊,所以對(duì)系統(tǒng)時(shí)鐘就有很高的要求,不僅需要有較高的頻率,而且還要有非常高的穩(wěn)定性,如果在FPGA的時(shí)鐘端直接加一高頻晶振,不僅時(shí)鐘不穩(wěn)定,而且功耗大,費(fèi)用高,在本設(shè)計(jì)中,直接調(diào)用Altera公司的PLL核,在FPGA時(shí)鐘端只需加一低頻晶振,通過(guò)FPGA內(nèi)部PLL倍頻達(dá)到系統(tǒng)時(shí)鐘要求,輸出的時(shí)鐘相位偏移在允許范圍內(nèi)。

2.3 DDS控制模塊

(1)頻率控制字輸入模塊

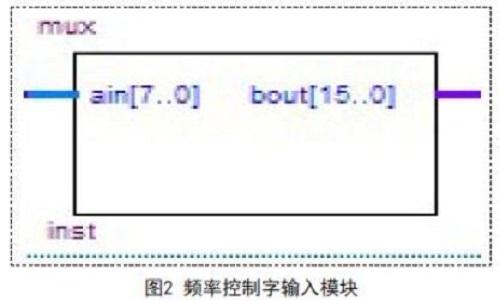

頻率控制字輸入模塊如圖2所示,數(shù)據(jù)選擇器控制輸入16位頻率控制字。

(2)步進(jìn)頻率控制模塊

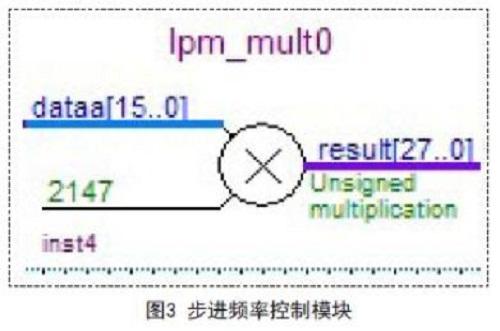

步進(jìn)頻率控制模塊如圖3所示,通過(guò)一個(gè)乘法器來(lái)控制步進(jìn)頻率,具體算法如下:f步進(jìn)=fc*2147/232.

通過(guò)改變乘法器的乘數(shù)來(lái)改變步進(jìn)頻率。要使步進(jìn)為1Hz那么乘法器的乘數(shù)為22.

(3)頻率累加器

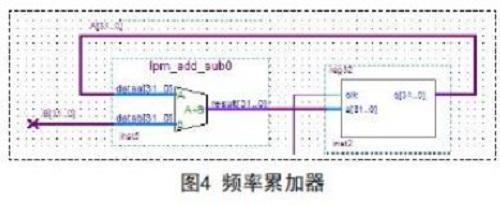

頻率累加器模塊如圖4所示,通過(guò)一個(gè)32位加法器跟32位寄存器構(gòu)成頻率累加器,頻率控制字高4位為0.

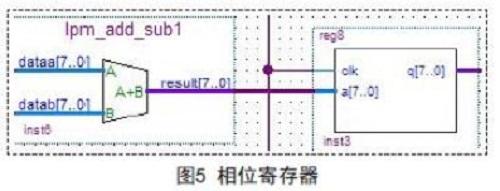

(4)相位寄存器

相位寄存器模塊如圖5所示,通過(guò)一個(gè)8位加法器跟8位寄存器構(gòu)成相位寄存器并產(chǎn)生8位波形數(shù)據(jù)地址。

評(píng)論