- 問題1:什么是DRAM、SRAM、SDRAM? 答:名詞解釋如下 DRAM--------動態隨即存取器,需要不斷的刷新,才能保存 ...

- 關鍵字:

DRAM SRAM SDRAM

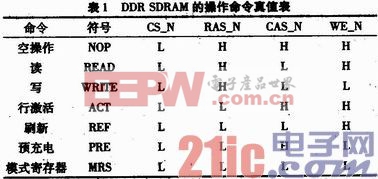

- 摘要 對DDR SDRAM的基本工作特性以及時序進行了分析與研究,基于FPGA提出了一種通用的DDRSDRAM控制器設計方案。在Modelaim上通過了軟件功能仿真,并在FPGA芯片上完成了硬件驗證。結果表明,該控制器能夠較好地完成DD

- 關鍵字:

控制器 設計 SDRAM DDR FPGA 基于

- 硬件電路 主控模塊的處理器采用三星公司的S3C2410,以其為核心擴展64MB的Nand-Flash和2MB的Nor-Flash用 ...

- 關鍵字:

車載信息 S3C2410 SDRAM

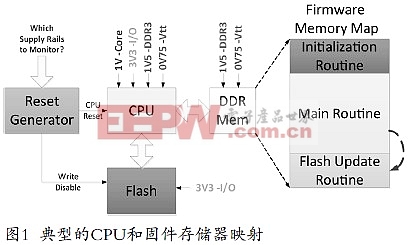

- 答案:兩個都是!閃存通常用于存儲嵌入式系統的固件。有時候,在某些系統的閃存中存儲的固件意外出錯,導致系統無法在上電后正常啟動。閃存出錯通常與軟件錯誤有關。然而,工程師們也普遍認同電源循環測試或者裕度測試增加了閃存出錯的可能性。當板上使用復雜的ASIC或SoC越多,閃存出錯的問題就會更嚴重。

- 關鍵字:

嵌入式 CPU DDR

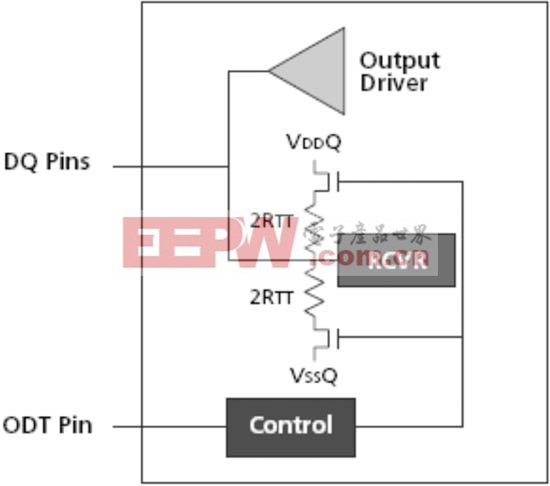

- 雙數據速率(DDR)接口在時鐘信號的上升沿和下降沿傳送數據,這種方法已經用來實現DDR、SDRAM、微處理器前端總線、Ultra-3 SCSI、AGP總線等的通信鏈路。在每個周期中,數據在時鐘的上升沿和下降沿采樣,最高數據傳輸速率一般是時鐘頻率的2倍。

- 關鍵字:

DDR 微處理器 數據傳輸

- 安捷倫科技公司(NYSE:A)日前宣布為其屢獲殊榮的 Infiniium 90000 X 系列示波器增添業界最高性能的混合信號示波器(MSO)功能。安捷倫不但推出了 6 種最新 MSO 型號,同時發布了13-GHz 帶寬的DSO 和 DSA 型號,進一步擴展了 X 系列示波器。

- 關鍵字:

安捷倫 示波器 DDR

- “幀像”技術是康佳平板電視在圖象顯示領域的革命性突破,“幀像”技術的基本原理是在刷新頻率為120HZ的屏幕...

- 關鍵字:

DDR 平板電視 幀像技術

- 摘要 本文章主要涉及到對DDR2和DDR3在設計印制線路板(PCB)時,考慮信號完整性和電源完整性的設計事項,這些是具有相當大的挑戰性的。文章重點是討論在盡可能少的PCB層數,特別是4層板的情況下的相關技術,其中

- 關鍵字:

DDR3 DDR 800 PCB

- 1 引言在高速信號處理系統中, 需要緩存高速、大量的數據, 存儲器的選擇與應用已成為系統實現的關鍵所在。DDR SDRAM是一種高速CMOS、動態隨機訪問存儲器, 它采用雙倍數據速率結構來完成高速操作。SDR SDRAM一個時鐘周

- 關鍵字:

Xilinx SDRAM FPGA DDR

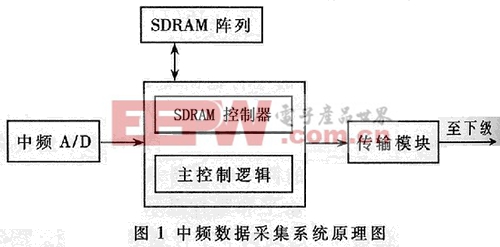

- 實現數據的高速大容量存儲是數據采集系統中的一項關鍵技術。本設計采用Altera 公司Cyclone系列的FPGA 完成了對DDR SDRAM 的控制,以狀態機來描述對DDR SDRAM 的各種時序操作,設計了DDR SDRAM 的數據與命令接口。用控

- 關鍵字:

SDRAM FPGA DDR 控制器

- 在高速實時或者非實時信號處理系統當中,使用大容量存儲器實現數據緩存是一個必不可少的環節,也是系統實現中的重點和難點之一。SDRAM(同步動態隨機訪問存儲器)具有價格低廉、密度高、數據讀寫速度快的優點,從而成

- 關鍵字:

實現 控制器 SDRAM VHDL 基于

- 全球領先的電子器件和系統設計、驗證和制造軟件及知識產權(IP)供應商新思科技公司(Synopsys, Inc., 納斯達克股票市場代碼:SNPS)日前宣布:其DesignWare DDR接口IP產品組合已經實現擴充,以使其包括了對基于新興的DDR4標準的下一代SDRAM。通過在一個單內核中就實現對DDR4、DDR3以及LPDDR2/3的支持,DesignWare DDR解決方案使設計師能夠在相同的系統級芯片(SoC)中,實現與高性能或者低功耗SDRAM的連接,它已經成為諸如用于智能手機和平板電腦的應用處理

- 關鍵字:

Synopsys SDRAM

- DR2(Double Data Rate 2,兩倍數據速率,版本2) SDRAM,是由JEDEC標準組織開發的基于DDR SDRAM的升級存儲技術。 相對于DDR SDRAM,雖然其仍然保持了一個時鐘周期完成兩次數據傳輸的特性,但DDR2 SDRAM在數據傳輸率、

- 關鍵字:

CPU 硬件 設計 MPC8548 基于 SDRAM 介紹 及其 DDR2

- 電子產品世界,為電子工程師提供全面的電子產品信息和行業解決方案,是電子工程師的技術中心和交流中心,是電子產品的市場中心,EEPW 20年的品牌歷史,是電子工程師的網絡家園

- 關鍵字:

DSP 存儲系統 SDRAM

- DDR2簡介從1998年的PC100到今天的DDR3,內存技術同CPU前端總線一道經歷著速度的提升及帶寬的擴展。雖然DDR3在當今已經量產與使用,DDR2在實際上還擔任著內存業界應用最廣泛最成熟的中流砥柱的角色。DDR2在DDR的基礎上

- 關鍵字:

DDR2 DDR 測試 力科

ddr-sdram介紹

您好,目前還沒有人創建詞條ddr-sdram!

歡迎您創建該詞條,闡述對ddr-sdram的理解,并與今后在此搜索ddr-sdram的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473