- RS碼是線性分組碼中一種典型的糾錯碼,既能糾正隨機錯誤,也能糾正突發錯誤,在現代通信領域越來越受到重視。文中介紹基于FPGA使用Verilog―HDL語言的RS(15,9)編碼器的設計方法,并在QuartusII 5.O軟件環境下進行了功能仿真,仿真結果與理論分析相一致,該設計方法對實現任意長度的RS編碼有重要參考價值。

- 關鍵字:

FPGA RS編碼器

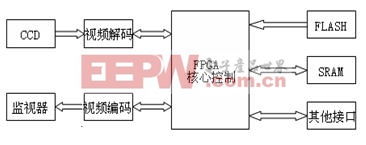

- 1、引言 視頻圖像采集是視頻信號處理系統的前端部分,正在向高速、高分辨率、高集成化、高可靠性方向發展。圖像采集系統在當今工業、軍事、醫學各個領域都有著極其廣泛的應用,如使用在遠程監控、安防、遠程抄

- 關鍵字:

設計 實現 系統 采集 FPGA 圖像 基于

- 推動FPGA調試技術改變的原因 進行硬件設計的功能調試時,FPGA的再編程能力是關鍵的優點。CPLD和FPGA早期使用時,如果發現設計不能正常工作,工程師就使用“調試鉤”的方法。先將要觀察的FPGA內部信號引到引腳,然

- 關鍵字:

FPGA 邏輯分析儀 調試

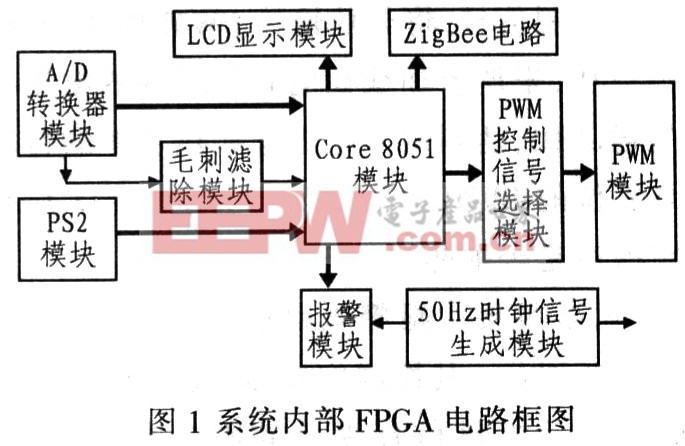

- 擴散爐溫度自動監控系統是對雙管擴散爐溫控部分進行改造,以提高爐溫精度,從而提高生產線的成品率,降低系統能耗。通過對Actel公司的Fusion系列器件FPGA編程實現系統的硬件控制。用C語言對Actel FPGA內置的8051軟核編程實現系統的軟件控制。整個監控系統完成數據采集、控制算法和ZigBee無線傳輸等功能。測試表明,采用Fusion FPGA設計.可以同時完成多路溫度控制,整個系統的控制精度也有進一步的提高。

- 關鍵字:

FPGA 設計 控制系統 自動 溫度 擴散 轉換器

- 1可重構測控系統的提出測控系統一般是指基于計算機實現數據采集和控制的系統。測控系統在工業現場控制、家...

- 關鍵字:

FPGA 測控系統 應用設計

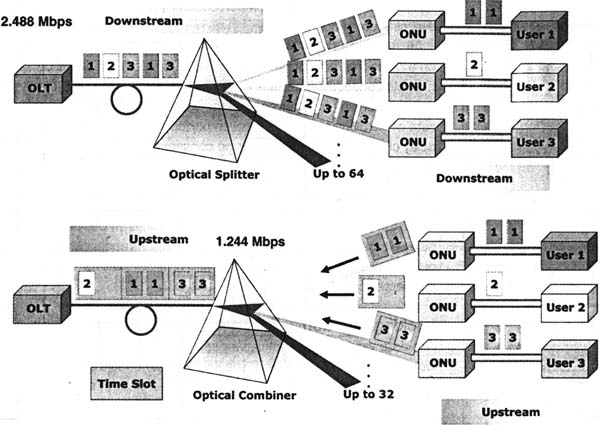

- 在2005年,FSAN(全業務接入網)組商定了千兆位無源光網絡(GPON)規范(見圖1)。此規范建立了語音、數據和視頻具有成本效益的遞交過程,這包括遞交到終端用戶的服務質量。‘first mile’接入技術采用光纖連接(光纖到用戶系統連接)可增加寬帶內容選擇。GPON很可能超過以太網無源光網絡成為未來光網絡的選擇。

- 關鍵字:

FSAN GPON FPGA

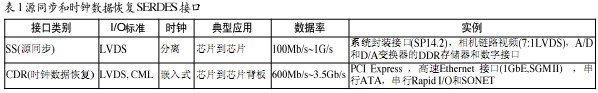

- 芯片功能的增加和數據吞吐量的要求,促使芯片行業從較低數據率的并行連接,轉向較高速度的串行連接。SERDES(Serializer-Dese rializer,)是經高速差分對,而不是經較低速度的并行總線傳輸串行化的數據。一個實例是用單個PCI-Express通道,替代傳統的32位、64MHz PCI總線(可達到2.112Gb/s),僅用4條線(運行在2.5GHz),可達到4Gb/s總數據率。簡言之,SERDES協議允許用較少的引腳數傳輸較高的數據率。

- 關鍵字:

SERDES FPGA

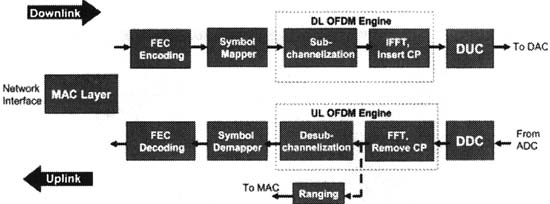

- 大量出現的無線應用具有嚴格的功耗設計要求和低價格。除功耗和低價設計任務外,還有高數據率要求和符合行業標準。系統設計師也需要保證最后產品的高性能和靈活性。

- 關鍵字:

IF FPGA OFDMA WiMAX

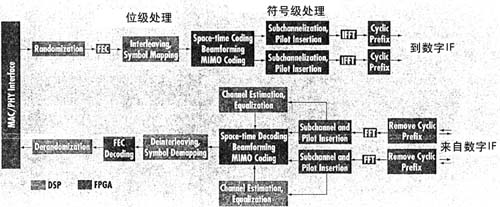

- FPGA和DSP之間的“智能配分”可使無線系統設計師獲得最佳性能組合和成本——效能。應用DSP和FPGA組合可使成本降低。對于無線基站,組合有DSP可編程邏輯的系統配分,可促使更大的產品設計和市場成功率。

- 關鍵字:

FPGA DSP

- 前言 計算機的并行接口一開始是作為打印機接口而設計的。隨著計算機周邊設備的不斷擴展,人們對提高計算機外設的數據采集速度的要求也越來越高。傳統的異步串行通訊方式雖然具有數據傳輸距離較遠的優勢,但是由于數據

- 關鍵字:

CPLD EPP 計算機并口 模式

- 隨著國民經濟的不斷發展,變頻調速裝置的應用越來越廣泛。如何打破國外產品的壟斷,已成為一個嚴肅的課題擺在我國工程技術人員的面前。

在某型號大功率變頻調速裝置中,由于裝置的尺寸較大,考慮到結構

- 關鍵字:

CPLD IGBT 驅動設計 中的應用

- 在數字通信系統中,必須以符號速率對解調器的輸出進行周期性地采樣.為此,接收器需要一個采樣時鐘信號,這個時鐘信號的頻率和符號速率相等,相位則必須保證采樣時刻是最佳的.在接收器中獲得這個采樣時鐘的過程被稱為符號

- 關鍵字:

FPGA 模糊控制 同步器

- 耗費數月精力做出的設計卻無法滿足時序要求,這確實非常令人傷心。然而,試圖正確地對設計進行約束以保證滿足時序要求的過程幾乎同樣令人費神。找到并確定時序約束本身通常也是非常令人頭痛的問題。時序問題的惱人之

- 關鍵字:

FPGA 發現 時序

cpld/fpga介紹

您好,目前還沒有人創建詞條cpld/fpga!

歡迎您創建該詞條,闡述對cpld/fpga的理解,并與今后在此搜索cpld/fpga的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473