基于FPGA的圖像采集系統(tǒng)設計與實現(xiàn)

1、引言

本文引用地址:http://www.104case.com/article/167049.htm視頻圖像采集是視頻信號處理系統(tǒng)的前端部分,正在向高速、高分辨率、高集成化、高可靠性方向發(fā)展。圖像采集系統(tǒng)在當今工業(yè)、軍事、醫(yī)學各個領域都有著極其廣泛的應用,如使用在遠程監(jiān)控、安防、遠程抄表、可視電話、工業(yè)控制、圖像模式識別、醫(yī)療器械等各個領域都有著廣泛的應用[1]。本文介紹了一種基于FPGA的圖像采集系統(tǒng),用戶可以根據(jù)需要對FPGA 內(nèi)部的邏輯模塊和I/O模塊重新配置,以實現(xiàn)系統(tǒng)的重構(gòu)[1][2];而且采用這種設計方案 ,便于及時地發(fā)現(xiàn)設計中的錯誤,能夠有效地縮短研發(fā)時間,提高工作效率。

2、系統(tǒng)的總體框架和工作原理

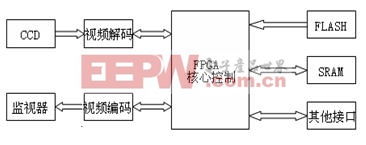

整個系統(tǒng)主要分為四個模塊:視頻解碼模塊、視頻編碼模塊、存儲器模塊和FPGA核心控制模塊,系統(tǒng)總體框架如圖1所示。

圖1 系統(tǒng)的總體框圖

其中FPGA實現(xiàn)的主要功能有:視頻編解碼器件的初始化,視頻圖像的采集存儲以及將采集的圖像數(shù)據(jù)通過視頻編碼芯片送到監(jiān)視器上顯示。

系統(tǒng)的工作原理為:系統(tǒng)上電后,F(xiàn)PGA通過FLASH中的程序?qū)ν瓿梢曨l解碼和編碼芯片的初始化配置;在接到視頻AD轉(zhuǎn)換的中斷信號后,F(xiàn)PGA將轉(zhuǎn)換的數(shù)字圖像數(shù)據(jù)傳送到SRAM保存;一幀圖像轉(zhuǎn)換結(jié)束后FPGA再將SRAM中的數(shù)字圖像傳遞給視頻編碼芯片以便在監(jiān)視器上顯示,同時開始控制下一幀圖像的采集。

3、硬件電路設計

3.1 AD和DA轉(zhuǎn)換模塊

本系統(tǒng)采用的視頻編解碼芯片是ADV7181和ADV7177,下面分別介紹AD和DA轉(zhuǎn)換器件的硬件電路設計。

3.1.1 AD轉(zhuǎn)換模塊

ADV7181系統(tǒng)是AD公司推出的一款視頻解碼芯片[3],它具有如下特點: I2C總線接口,6通道模擬視頻輸入,支持NTSC、PAL、SECAM視頻制式,支持多種模擬輸入格式和多種數(shù)字輸出格式。

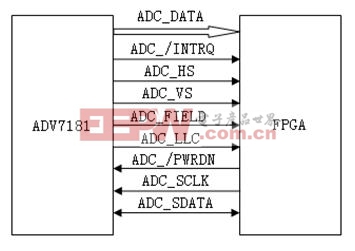

本系統(tǒng)中選用其中的通道1作為PAL制CVBS視頻輸入,數(shù)據(jù)輸出可根據(jù)需要采用8位或16位的格式輸出。ADV7181與FPGA的接口電路如圖2所示。

圖2 ADV7181與FPGA的接口電路

系統(tǒng)上電后通過FPGA的I2C模塊完成對ADV7181的初始化配置,其中ADC_SCLK、ADC_SDATA分別為I2C總線的時鐘線和數(shù)據(jù)線。ADV7181正常工作后分別輸出水平同步信號ADV_HS、垂直同步信號ADV_VS、 場同步信號ADV_FIELD、中斷信號ADC_/INTRQ、ADC_LLC同步信號和圖像數(shù)據(jù)信號ADC_DATA(8位或16位可配置輸出),另外ADC_/PWRDN信號控制ADV7181是否工作于省電模式。用戶可以根據(jù)需要選擇水平、垂直和場同步信號(CCIR-601格式)或ADC¬_LLC信號(CCIR-656格式)來實現(xiàn)系統(tǒng)與視頻輸入的同步,并利用這些同步信號控制對轉(zhuǎn)換完成的視頻數(shù)據(jù)的寫存儲器操作。

3.1.2 DA轉(zhuǎn)換模塊

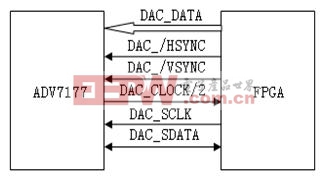

DA轉(zhuǎn)換采用的是AD公司的ADV7177[4],它具有如下特點:I2C接口,3路模擬視頻輸出,支持多種數(shù)字輸入格式和多種模擬輸出格式,用戶可根據(jù)需要選擇使用。它的電路設計與ADV7181類似,ADV7177與FPGA的接口電路如圖3所示。

圖3 ADV7177與FPGA的接口電路

其中DAC_DATA為輸入數(shù)字視頻信號,DAC_/HSYNC、DAC_/VSYNC分別為水平和垂直同步信號,DAC_CLOCK2為ADV7177輸出的27M或13.5M同步時鐘( 與寄存器的配置數(shù)據(jù)有關),DAC_SCLK、DAC_SDATA為ADV7177的I2C配置總線。

3.2 FPGA核心控制模塊

FPGA核心控制模塊采用的是ALTERA公司Cyclone II系列的EP2C20[5],它具有較高的性價比:EP2C20最多用戶管腳數(shù)為315,四個PLL,26個嵌入式18*18乘法器,52個M4K RAM塊,186752個邏輯單元;共分8個I/O Bank,每個Bank可以根據(jù)需要配置為1.2V或3.3V的I/O電平,方便與外圍電路連接。考慮到系統(tǒng)的實際需求,在該系統(tǒng)中采用具有240個引腳PQFP封裝的EP2C20Q240。

在該系統(tǒng)中,F(xiàn)PGA主要完成對視頻AD、DA的初始化配置和存儲器的讀寫控制,它通過AD的中斷信號完成對視頻數(shù)據(jù)的采集,并將采集的數(shù)據(jù)放到存儲模塊中,當采集完一幀后將數(shù)據(jù)傳遞給視頻編碼芯片并在監(jiān)視器上顯示同時開始采集下一幀圖像。

在本系統(tǒng)中FPGA采用了JTAG和AS兩種配置模式,具體的設計可參考ALTERA數(shù)據(jù)手冊[5]。

3.3 存儲器及其他模塊

由于FPGA芯片內(nèi)部的RAM資源有限,不能存儲過多的視頻數(shù)據(jù)并對其進行處理,因此在本系統(tǒng)設計中,外加了兩片SRAM芯片來輔助FPGA進行視頻信號采集。兩片SRAM可以進行16位的數(shù)據(jù)存儲,這樣ADV7181和ADV7177可以根據(jù)需要配置為8位或16位數(shù)據(jù)的工作模式,提高了系統(tǒng)的靈活性。

本系統(tǒng)設計中采用的SRAM芯片是美國IDT公司生產(chǎn)的IDT71V424[6],它是采用高性能與可靠性的CMOS工藝生產(chǎn)的高速靜態(tài)存儲器,其單片存儲容量為512K*8Bit,具有高速的訪問時間,10或12ns。其內(nèi)部完全由靜態(tài)異步電路構(gòu)成,無需輸入時鐘信號,也不必對芯片進行刷新,即可直接對無用數(shù)據(jù)進行覆蓋。

在實際的設計中為了保證控制信號的有效性,3條控制線SRAM_/WE、SRAM_/OE, SRAM_/CS分別加了一個4.7K的上拉電阻后才與FPGA芯片連接。具體電路如圖4所示:

圖4 SRAM與FPGA的接口電路

此外,為了減少模擬與數(shù)字系統(tǒng)之間的相互干擾,電源模塊采用的是數(shù)字電源和模擬電源分開設計最后一點共地的設計方案。主要采用了TI公司的TPS54612、TPS64616分別提供FPGA 1.2V核心電壓和3.3V IO電壓;模擬1.8V和3.3V采用的是AMS1117系列的電源芯片。

4、系統(tǒng)軟件設計

本系統(tǒng)軟件是在Quartus II 環(huán)境下采用Verilog語言開發(fā)完成的。主要包括:1、AD和DA芯片的初始化配置,2、視頻圖像的采集,3、視頻圖像的存儲與DA轉(zhuǎn)換。

評論