EEPW首頁(yè) >>

主題列表 >>

cadence?

cadence? 文章 最新資訊

Cadence臺(tái)積電微軟以云計(jì)算縮減IC設(shè)計(jì)驗(yàn)證時(shí)間

- Cadence Design Systems, Inc.宣布與臺(tái)積電及微軟三方合作之成果。該合作的重點(diǎn)是利用云端基礎(chǔ)架構(gòu)來縮短半導(dǎo)體設(shè)計(jì)簽核時(shí)程。透過此合作,客戶將可藉由微軟 Azure上的Cadence CloudBurst平臺(tái),采用臺(tái)積電技術(shù)的Cadence Tempus時(shí)序簽核解決方案及Quantus提取解決方案,獲得加速完成時(shí)序簽核的途徑。臺(tái)積電設(shè)計(jì)建構(gòu)管理處資深處長(zhǎng)Suk Lee表示:「半導(dǎo)體研發(fā)人員正以先進(jìn)的制程技術(shù)來實(shí)現(xiàn)與滿足超過其功率及效能上的要求。但在日益復(fù)雜的先進(jìn)制程簽核要求下,使得實(shí)

- 關(guān)鍵字: Cadence 臺(tái)積電 微軟 IC設(shè)計(jì)

Cadence與聯(lián)電合作開發(fā)28納米HPC+工藝中模擬/混合信號(hào)流程的認(rèn)證

- 聯(lián)華電子今(6日)宣布Cadence?模擬/混合信號(hào)(AMS)芯片設(shè)計(jì)流程已獲得聯(lián)華電子28納米HPC+工藝的認(rèn)證。 透過此認(rèn)證,Cadence和聯(lián)電的共同客戶可以于28納米HPC+工藝上利用全新的AMS解決方案,去設(shè)計(jì)汽車、工業(yè)物聯(lián)網(wǎng)(IoT)和人工智能(AI)芯片。 此完整的AMS流程是基于聯(lián)電晶圓設(shè)計(jì)套件(FDK)所設(shè)計(jì)的,其中包括具有高度自動(dòng)化電路設(shè)計(jì)、布局、簽核及驗(yàn)證流程的一個(gè)實(shí)際示范電路,讓客戶可在28納米的HPC+工藝上實(shí)現(xiàn)更無縫的芯片設(shè)計(jì)。Cadence AMS流程結(jié)合了經(jīng)客制化確認(rèn)的類比

- 關(guān)鍵字: Cadence 聯(lián)電 28納米HPC 工藝中模擬/混合信號(hào) 流程認(rèn)證

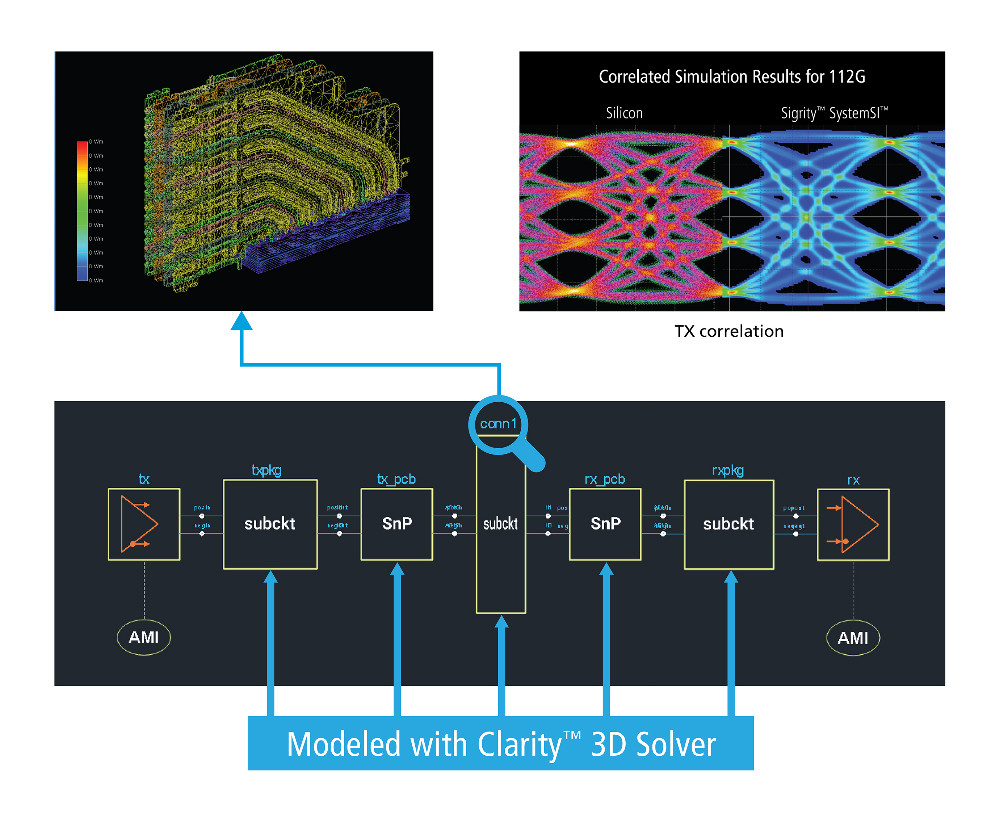

Cadence推出Clarity 3D場(chǎng)求解器,為系統(tǒng)級(jí)分析和設(shè)計(jì)提供前所未有的性能及容量

- 內(nèi)容提要: ? Clarity 3D Solver場(chǎng)求解器是Cadence系統(tǒng)分析戰(zhàn)略的首款產(chǎn)品,電磁仿真性能比傳統(tǒng)產(chǎn)品提高10倍,并擁有近乎無限的處理能力,同時(shí)確保仿真精度達(dá)到黃金標(biāo)準(zhǔn) ? 全新的突破性的架構(gòu)針對(duì)云計(jì)算和分布式計(jì)算的服務(wù)器進(jìn)行優(yōu)化,使得仿真任務(wù)支持調(diào)用數(shù)以百計(jì)的CPU進(jìn)行求解 ? 真正的3D建模技術(shù),避免傳統(tǒng)上為了提高仿真效率而人為對(duì)結(jié)構(gòu)進(jìn)行剪切帶來的仿真精度降低的風(fēng)險(xiǎn) ? 輕松讀取所有標(biāo)準(zhǔn)芯片和IC封裝平臺(tái)的設(shè)計(jì)數(shù)據(jù),并與Cadence設(shè)計(jì)平臺(tái)實(shí)現(xiàn)專屬集成

- 關(guān)鍵字: Cadence Cadence? Clarity? 3D Solver場(chǎng)求解器

Arm、Cadence、Xilinx聯(lián)合推出基于TSMC 7納米工藝的首款A(yù)rm Neoverse系統(tǒng)開發(fā)平臺(tái),面向下一代云到邊緣基礎(chǔ)設(shè)施

- 中國(guó)上海,2019年3月13日—Arm、Cadence Design Systems, Inc. (NASDAQ: CDNS) 和Xilinx, Inc. (NASDAQ: XLNX)今日宣布,聯(lián)合推出基于全新Armò Neoverse? N1的系統(tǒng)開發(fā)平臺(tái),該平臺(tái)將面向下一代云到邊緣基礎(chǔ)設(shè)施,并已在TSMC(TWSE: 2330, NYSE: TSM) 7納米FinFET工藝上得到全面硅驗(yàn)證。Neoverse N1 系統(tǒng)開發(fā)平臺(tái)(SDP)同時(shí)也是業(yè)內(nèi)第一個(gè)7納米基礎(chǔ)設(shè)施開發(fā)平臺(tái),可利

- 關(guān)鍵字: Arm Cadence Xilinx

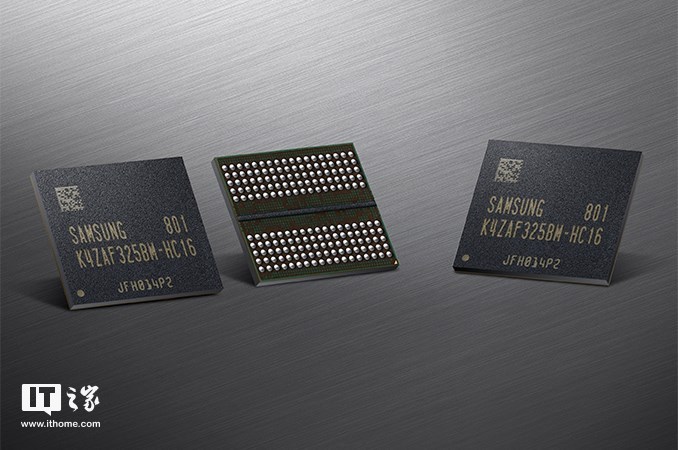

Cadence宣布流片GDDR6芯片:基于三星7LPP,不僅用于顯卡

- 根據(jù)外媒報(bào)道,Cadence宣布已成功在三星的7LPP制造工藝中流片其GDDR6 IP芯片。 Cadence的GDDR6 IP解決方案包括該公司的Denali內(nèi)存控制器,物理接口和驗(yàn)證IP。控制器和PHY的額定值可處理每個(gè)引腳高達(dá)16 Gbps的數(shù)據(jù)傳輸速率,并具有低誤碼率(BER)功能,可降低內(nèi)存總線上的重試次數(shù),從而縮短延遲,從而確保更大的內(nèi)存帶寬。IP封裝以Cadence的參考設(shè)計(jì)提供,允許SoC開發(fā)人員快速?gòu)?fù)制IP設(shè)計(jì)人員用于其測(cè)試芯片的實(shí)現(xiàn)。 傳統(tǒng)上,GDDR內(nèi)存主要用于顯卡,但

- 關(guān)鍵字: Cadence GDDR6

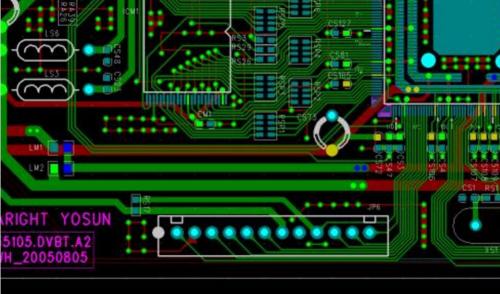

4周小白成為大神,速成Cadence Allegro 讓你走向職場(chǎng)巔峰!

- 一、PCB工程師目前現(xiàn)狀 近年來,隨著工業(yè)4.0戰(zhàn)略的實(shí)施,智能硬件的加速崛起,PCB工程師更是成為了未來最有前途的職業(yè)之一。特別是電子工業(yè)的不斷壯大,使得產(chǎn)品研發(fā)周期不斷縮短、信號(hào)速率不斷提高、單板密度越來越大、門電路工作電壓越來越低、SI-PI-EMI問題趨于復(fù)雜,這樣就要求PCB設(shè)計(jì)工程師必須提高專業(yè)素養(yǎng),也使得PCB設(shè)計(jì)的工作日益成為電子設(shè)計(jì)中獨(dú)立而又不可缺失的一環(huán)。 二、作為一名Allegro工程師 面對(duì)電子設(shè)備這些高性能、高速、高密、輕薄的趨勢(shì),高速信號(hào)的PCB設(shè)計(jì),越來越成為電子硬

- 關(guān)鍵字: Cadence

EDA的低功耗游戲

- 隨著芯片設(shè)計(jì)轉(zhuǎn)移到90nm和65nm,芯片制造商面臨著新的挑戰(zhàn)包括溫度、穩(wěn)定性及電源可靠性或電源效率的差異性等方面的挑戰(zhàn)。業(yè)界試圖通過幾種途徑努力來

- 關(guān)鍵字: EDA技術(shù) 芯片設(shè)計(jì) Cadence

Cadence Sigrity 2018最新版集成3D設(shè)計(jì)與分析,大幅縮短PCB設(shè)計(jì)周期

- 楷登電子(美國(guó)Cadence公司,NASDAQ: CDNS)今日宣布發(fā)布Cadence? Sigrity? 2018版本,該版本包含最新的3D解決方案,幫助PCB設(shè)計(jì)團(tuán)隊(duì)縮短設(shè)計(jì)周期的同時(shí)實(shí)現(xiàn)設(shè)計(jì)成本和性能的最優(yōu)化。 獨(dú)有的3D設(shè)計(jì)及分析環(huán)境,完美集成了Sigrity工具與Cadence Allegro?技術(shù),較之于當(dāng)前市場(chǎng)上依賴于第三方建模工具的產(chǎn)品,Sigrity? 2018版本可提供效率更高、出錯(cuò)率更低的解決方案,大幅度縮短設(shè)計(jì)周期的同時(shí)、降低設(shè)計(jì)失誤風(fēng)險(xiǎn)。 此外,全新的3D Workbench

- 關(guān)鍵字: Cadence,PCB

Cadence Innovus助力Realtek成功開發(fā)DTV SoC解決方案

- 楷登電子(美國(guó)Cadence公司)今日宣布,瑞昱半導(dǎo)體股份有限公司(Realtek Semiconductor Corp.)將 Cadence? Innovus? 設(shè)計(jì)實(shí)現(xiàn)系統(tǒng)用于其最新 28nm 數(shù)字電視(DTV)系統(tǒng)級(jí)芯片的研發(fā)并成功流片,同時(shí)成功縮小了芯片面積并降低了功耗。除了改善結(jié)果質(zhì)量(QoR)之外,Innovus 設(shè)計(jì)實(shí)現(xiàn)系統(tǒng)容量更高,可支持實(shí)現(xiàn)更大的頂層模塊,降低 SoC 頂層設(shè)計(jì)的分割區(qū)

- 關(guān)鍵字: Cadence SoC

PCB layout用啥軟件比較好?Cadence or AD?

- PCB layout是什么 PCB layout是印刷電路板。 印刷電路板同時(shí)也叫印制電路板,是一種讓各類電子元件實(shí)現(xiàn)有規(guī)則連接的載體。 PCB layout中文翻譯為印制板布局,傳統(tǒng)工藝上的電路板是利用印刷蝕刻出線路的方式,因此稱之為印刷或印制電路板。利用印制板人們不僅能夠避免安裝過程接線錯(cuò)誤(在PCB出現(xiàn)前,電子元件都是通過導(dǎo)線連接,不僅錯(cuò)綜雜亂還存在安全隱患)。最早使用PCB的是一個(gè)奧地利人叫保羅。愛斯勒,于1936年首次在收音機(jī)中使用。廣泛應(yīng)用出現(xiàn)在20世紀(jì)

- 關(guān)鍵字: Cadence PCB

Cadence Virtuoso定制IC設(shè)計(jì)平臺(tái)助力WillSemi提升模擬IC設(shè)計(jì)的穩(wěn)健性和交付速度

- 楷登電子(美國(guó)Cadence公司)今日宣布,WillSemi采用Cadenceò Virtuosoò 定制集成電路設(shè)計(jì)平臺(tái),增強(qiáng)了模擬集成電路設(shè)計(jì)的可靠性,并縮短了產(chǎn)品的總體上市時(shí)間。較此前部署的行業(yè)解決方案,WillSemi采用Cadence定制集成電路設(shè)計(jì)流程不僅將模擬設(shè)計(jì)和實(shí)現(xiàn)時(shí)間減半,總設(shè)計(jì)周期時(shí)間也縮短了三分之一。 Cadence定制設(shè)計(jì)流程工具幫助WillSemi集成電路設(shè)計(jì)團(tuán)隊(duì)實(shí)現(xiàn)了如下目標(biāo): · 采用Virtuoso電路原理圖編輯器與Virtuoso版

- 關(guān)鍵字: Cadence Virtuoso

日月光2017年?duì)I收增長(zhǎng)12%,預(yù)計(jì)Q2營(yíng)收將逐季成長(zhǎng)

- 封測(cè)大廠日月光2月1日召開法說會(huì),展望2018年首季營(yíng)運(yùn),日月光預(yù)期以美元計(jì)價(jià)的封測(cè)營(yíng)收,將略高于去年同期12.3億美元,毛利率將略高于去年同期的23%。電子代工(EMS)合并營(yíng)收將略低于去年第三季331億元,毛利率將略高于上季9.2%。 2017年日月光集團(tuán)自結(jié)合并營(yíng)收創(chuàng)2904.41億元新臺(tái)幣新高,年增6%。毛利率18.2%、營(yíng)益率8.7%,低于前年19.3%、9.7%。歸屬業(yè)主稅后凈利229.88億元新臺(tái)幣,年增6%,創(chuàng)歷史次高,受股本膨脹影響,每股盈余2.82元新臺(tái)幣,與前年追溯調(diào)整后相

- 關(guān)鍵字: Cadence 存儲(chǔ)器

cadence?介紹

您好,目前還沒有人創(chuàng)建詞條cadence?!

歡迎您創(chuàng)建該詞條,闡述對(duì)cadence?的理解,并與今后在此搜索cadence?的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)cadence?的理解,并與今后在此搜索cadence?的朋友們分享。 創(chuàng)建詞條

熱門主題

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司