楷登電子(美國Cadence 公司)今日宣布,業界首款支持全新 PCI Express ? (PCIe?)5.0 架構的驗證 IP(VIP)正式可用。結合 TripleCheck? 技術,Cadence? VIP 旨在幫助設計師快速執行基于 PCIe 5.0 標準的服務器和存儲器的系統級芯片(SoC)設計的完整功能性驗證,確保產品功能符合設計初衷。 如需進一步了

關鍵字:

Cadence IP

楷登電子(美國Cadence 公司, NASDAQ:CDNS)今日宣布,業界首款支持全新 PCI Express ® (PCIe®)5.0 架構的驗證 IP(VIP)正式可用。結合 TripleCheck™ 技術,Cadence® VIP 旨在幫助設計師快速執行基于 PCIe 5.0 標準的服務器和存儲器的系統級芯片(SoC)設計的完整功能性驗證,確保產品功能符合設計初衷。

如需進一步了解基于PCIe 5.0架構并采用TripleCheck技術的Cadence

關鍵字:

Cadence PCI

中國的半導體產業持續呈現超過20%的成長率,而全球只有約5%。在中國建立本土化的公司,這對Cadence來說是個很重要的決定,從一年前開始討論這個問題,最后決定選址南京...

2017年11月13日,江蘇南京,Cadence與南京市浦口區人民政府簽署了為建立Cadence (中國)半導體產業基地的戰略合作備忘錄及中國IC知識產權(IP)開發與服務平臺的正式投資協定。

此次簽約儀式受到中國半導體業界的廣泛關注,100多位嘉賓現場出席和見證了儀式。

江蘇省省委常委、南京市市委書記張敬華代

關鍵字:

Cadence EDA

11月13日,電子設計自動化(EDA)與半導體知識產權(IP)的領先供應商美國楷登電子(Cadence)與南京市浦口區人民政府正式簽署戰略合作備忘錄以及投資協議。據悉,Cadence 項目是南京市浦口區繼引進臺積電之后在集成電路設計領域引進的又一個龍頭性項目,歷經兩年的洽談,在多方的共同努力下,今天終于簽約落地。

南京市江北新區管委會常務副主任、浦口區區委書記瞿為民先生致辭表示,此次簽約儀式標志著南京市浦口區與 Cadence 雙方的戰略投資進入實質性階段。南京江北新區是江蘇省唯一的國家級新區,

關鍵字:

Cadence 臺積電

楷登電子(美國Cadence 公司)今日與Arm聯合發布基于Arm? 服務器的Xcelium? 并行邏輯仿真平臺,這是電子行業內首個低功耗高性能的仿真解決方案。 在芯片制造之前, SoC芯片功能正確性驗證占用了整個項目70%的EDA軟件使用資源,這一需求促進了數據中心的增長。運行于ARM服務器的Xcelium仿真可帶來功耗顯著降低和仿真容量的顯著提升,可執行高吞吐和長周期測試,縮減了整個SoC驗證的時間和成本。 作為Cadence驗證套件(Cadence&n

關鍵字:

Cadence Xcelium

楷登電子(美國Cadence公司)今日宣布,其全流程數字簽核工具和Cadence? 驗證套裝的優化工作已經發布,支持最新Arm? Cortex?-A75和Cortex-A55 CP,基于Arm DynamIQ?技術的設計,及Arm Mali?-G72 GPU,可廣泛用于最新一代的高端移動應用、機器學習及消費電子類芯片。為加速針對Arm最新處理器的設計,Cadence為Cortex-A75和Cortex-A55 CPU量身開發全新7n

關鍵字:

Cadence Arm

楷登電子(美國Cadence公司)宣布即將于8月22日(星期二)在上海浦東嘉里大酒店舉辦一年一度的中國用戶大會——CDNLive China 2017。以“聯結,分享,啟發!”為主題的CDNLive大會將集聚超過1000位IC行業從業者,包括IC設計工程師、系統開發者與業界專家,將分享重要半導體設計領域的解決方案和成功經驗,讓參與者獲得知識、靈感與動力,并為實現高階半導體芯片、SoC設計和系統挑戰提供解決方案。詳細的會議信息及報名請瀏覽www.cdnlive.com CDNLiv

關鍵字:

Cadence CDNLive

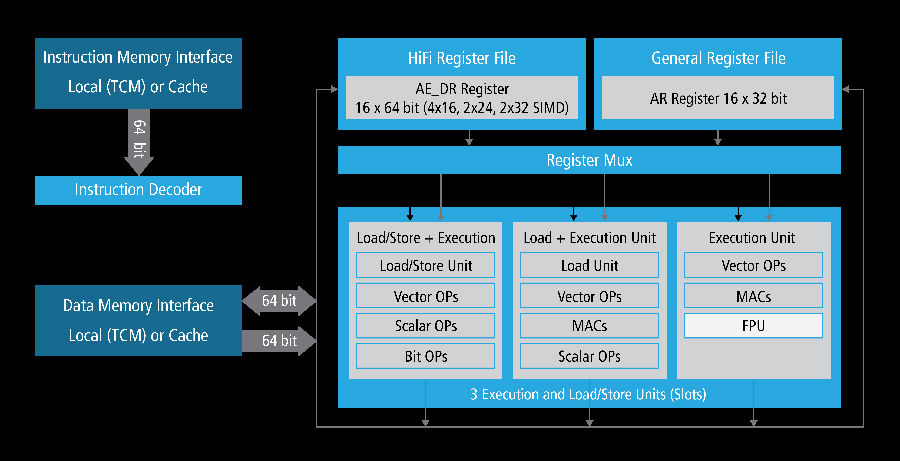

楷登電子(美國 Cadence 公司)今天宣布推出針對最新移動和家庭娛樂應用中系統級芯片(SoC)設計的Cadence? Tensilica? HiFi 3z DSP IP內核 。其應用包括智能手機、增強現實(AR)/ 3D眼鏡、數字電視和機頂盒(STB)等。比較在業界音頻DSP內核發貨量站主導地位的前一代產品HiFi 3 DSP ,新的HiFi 3z架構將可提供超過1.3

關鍵字:

Cadence DSP

做芯片設計的各位,在某個時刻,你也許會產生一個想法,“為什么不自己設計一個處理器呢?”或許是手頭的處理器并不好用;或許是想用的處理器貴的離譜;或許是你希望做出差異化的產品;又或者僅僅因為它是個誘人的挑戰,你想嘗試一下...既然如此,我很高興能和你討論一下怎么完成這個任務。 交付物 我們先從結果說起,也就是這項任務的最終交付物。這里不妨參考ARM處理器核的deliverables。當然,如果只是一個自己用的專用處理器,不一定要有這么完整的交付物。 硬件:主要是處理器相關的RTL代碼,驗證環境,ED

關鍵字:

專用處理器 Cadence

楷登電子(美國Cadence公司)今日正式發布全新VirtualBridge?適配器。較傳統RTL仿真,基于虛擬仿真技術的VirtualBridge?適配器可以加速硅前驗證階段的軟件初啟。同時,VirtualBridge適配器與傳統在線(In-Circuit)仿真應用模式互為補充,通過Cadence? Palladium? Z1企業級仿真平臺,可以讓軟件設計師提前3個月開始進行硅前軟件驗證工作。如需了解更多內容,請訪問www.cadence.com/go/virtualbridge

關鍵字:

Cadence VirtualBridge

楷登電子(美國Cadence公司)今日發布全新Cadence? Virtuoso? System Design Platform(Virtuoso系統設計平臺),結合Cadence Virtuoso平臺與Allegro? 及Sigrity?技術,打造一個正式的、優化的自動協同設計與驗證流程。多項跨平臺技術的高度集成幫助設計工程師實現芯片、封裝和電路板的同步和協同設計。這一過程在此之前只能通過手動完成,全新Virtuoso系統設計平臺可以實現流

關鍵字:

Cadence Virtuoso

楷登電子(美國Cadence公司)今日正式發布JasperGold? 形式驗證平臺擴展版,引入高級形式化驗證技術的JasperGold Superlint和Clock Domain Crossing (CDC)應用,以滿足JasperGold形式驗證技術在RTL設計領域的簽核要求。較現有驗證解決方案,Superlint和CDC應用提高了IP設計質量,后期RTL變更最高減少80%, IP開發時間縮短4周。如需了解更多關于JasperGold技術

關鍵字:

Cadence RTL

楷登電子(美國 Cadence 公司) 今日宣布其數字、簽核與定制/模擬工具成功在三星電子公司7LPP和8LPP工藝技術上實現。較前代高階工藝節點FinFET技術,7LPP和8LPP工藝技術不僅進一步優化了功耗、性能和面積特性,擴展能力也更為出色。目前,客戶已經可以應用下一代技術開始早期設計。 Cadence定制/模擬、數字和簽核工具全面滿足三星工藝需求,支持實現7LPP和8LPP工藝技術;三星客戶可開發各類復雜的高階節點設計,充分滿足移動市場和其他垂直市場的應用需求。

關鍵字:

Cadence 7LPP

作者 王瑩 近日,Cadence發布了首款面向汽車、監控、無人機和移動市場的神經網絡DSP IP,引起了業界的關注。 Cadence公司Tensilica事業部資深市場群總監Steve Roddy專程來到北京,向媒體介紹其特點。 在神經網絡的器件方面,英偉達主宰了通用GPU。此次Cadence Tensilica發布的神經網絡DSP IP則是面向嵌入式芯片。 通常其他友商的方案是面向一個卷積神經網絡(CNN)層,而最新的Cadence Tensilica Vision C5 DSP由于可配置,可以面

關鍵字:

Cadence 神經網絡DSP IP Steve Roddy 201706

近日,Cadence發布了首款面向汽車、監控、無人機和移動市場的神經網絡DSP?IP,引起了業界的關注。 實際上,多家公司正在推出或研制神經網絡IP、c/解決方案。Cadence的方案有何優勢?Cadence公司Tensilica事業部資深市場群總監Steve?Roddy為此專程來到北京,向媒體介紹其特點。 Vision?C5概況 在神經網絡的器件方面,英偉達主宰了通用GPU。此次Cadence?Tensilica發布的神經網絡DSP?IP則是面

關鍵字:

Cadence 芯片

cadence?介紹

您好,目前還沒有人創建詞條cadence?!

歡迎您創建該詞條,闡述對cadence?的理解,并與今后在此搜索cadence?的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473