靜態(tài)隨機存儲器(sram) 文章 最新資訊

全球首個22納米節(jié)點靜態(tài)存儲單元研制成功

- 美國IBM公司、AMD以及紐約州立大學(xué)Albany分校的納米科學(xué)與工程學(xué)院(CNSE)等機構(gòu)共同宣布,世界上首個22納米節(jié)點靜態(tài)存儲單元(SRAM)研制成功。這也是全世界首次宣布在300毫米研究設(shè)備環(huán)境下,制造出有效存儲單元。 22納米節(jié)點靜態(tài)存儲單元SRAM芯片是更復(fù)雜的設(shè)備,比如微處理器的“先驅(qū)”。SRAM單元的尺寸更是半導(dǎo)體產(chǎn)業(yè)中的關(guān)鍵技術(shù)指標。最新的SRAM單元利用傳統(tǒng)的六晶體管設(shè)計,僅占0.1平方微米,打破了此前的SRAM尺度縮小障礙。 新的研究工作是在紐

- 關(guān)鍵字: IBM SRAM 22納米 32納米

瑞薩推出高速SRAM*1產(chǎn)品系列

- 瑞薩科技公司(以下簡稱“瑞薩”)宣布推出面向新一代通信網(wǎng)絡(luò)內(nèi)高端路由器和交換機使用的高速SRAM*1產(chǎn)品系列。這些SRAM產(chǎn)品不僅符合QDR聯(lián)盟*2行業(yè)標準要求,還實現(xiàn)了72Mb四倍數(shù)據(jù)速率II+(QDRTM II+)和雙數(shù)據(jù)速率II+(DDRII+)的業(yè)內(nèi)最高工作速度,并且包含72Mb QDRII和DDRII SRAM器件。整個器件系列(具有多種速度和配置)將于2009年8月在日本開始陸續(xù)進行銷售。 新產(chǎn)品特性如下: (1) 業(yè)內(nèi)最高的工作速度:533 MHz(Q

- 關(guān)鍵字: 瑞薩 SRAM DDRII

臺積電率先推出28納米低耗電平臺

- 臺灣積體電路制造股份有限公司今(17)日宣布領(lǐng)先專業(yè)積體電路制造服務(wù)領(lǐng)域,成功開發(fā)28納米低耗電技術(shù),同時配合雙/三閘極氧化層(dual/triple gate oxide)工藝,將32納米工藝所使用的氮氧化硅(Silicon Oxynitride,SiON))/多晶硅(poly Si)材料延伸至28納米工藝,使得半導(dǎo)體可以持續(xù)往先進工藝技術(shù)推進。此一工藝技術(shù)的優(yōu)勢還包括高密度與低Vcc_min六電晶體靜態(tài)隨機存取記憶體(SRAM)元件、低漏電電晶體、已通過驗證的傳統(tǒng)類比/射頻/電子熔線(analog

- 關(guān)鍵字: 臺積電 SRAM 28納米 低耗電 氮氧化硅 多晶硅

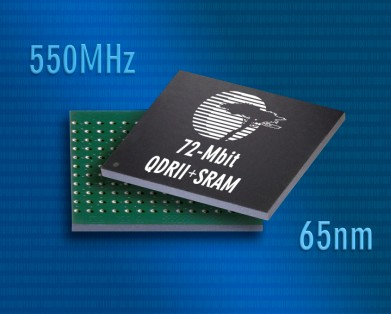

賽普拉斯推出采用 65 納米工藝技術(shù)的 SRAM

- 賽普拉斯-SRAM 領(lǐng)域的業(yè)界領(lǐng)先公司,日前宣布,該公司在業(yè)界率先推出采用 65 納米線寬的 Quad Data Rate™ (QDR™) 和 Double Data Rate (DDR) SRAM 器件樣品。新推出的 72-Mbit QDRII、QDRII+、DDRII 和 DDRII+ 存儲器采用了賽普拉斯合作伙伴制造商 UMC 開發(fā)的工藝技術(shù)。新型 SRAM 實現(xiàn)了目前市場上最快的 550 MHz時鐘速度,在 36 位 I/O 寬度的 QDRII+ 器件中可實現(xiàn)高達 80

- 關(guān)鍵字: 賽普拉斯 納米 SRAM

賽普拉斯半導(dǎo)體公司推出的三款SRAM新品

- 2009年4月8日,北京訊,日前,賽普拉斯半導(dǎo)體公司宣布推出了一款低功耗 SRAM 和兩款快速異步 SRAM,進一步豐富了其業(yè)界領(lǐng)先的產(chǎn)品系列。新型的 64 兆比特 (Mbit) MoBL® (More Battery Life™) SRAM 是市場上密度最大的低功耗 SRAM,旨在延長高端銷售點終端、游戲應(yīng)用、VoIP 電話、手持消費和醫(yī)療設(shè)備等應(yīng)用的電池工作時間。新推出的 3 兆比特和6兆比特快速異步 SRAM 與 24 位寬的處理器相連接,能充分滿足音頻處理、無線和網(wǎng)絡(luò)等應(yīng)用

- 關(guān)鍵字: Cypress SRAM

基于SRAM的FPGA連線資源的一種可測性設(shè)計

- 本文提出在FPGA芯片內(nèi)插入多條移位寄存器鏈的方法,可使測試開關(guān)盒連線資源的時問比傳統(tǒng)的測試方法和已有的一種方法時間上減少了99%以上,大大降低了測試的時間,降低了測試成本,并且消耗的硬件面積比大約在5%左右,在可接受的范圍內(nèi)。

- 關(guān)鍵字: SRAM FPGA 資源 可測性設(shè)計

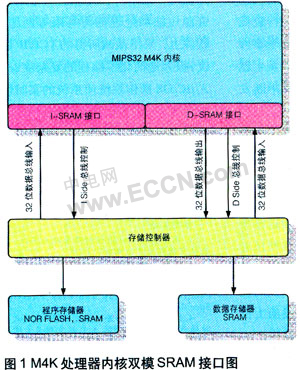

MIPS32 M4K處理器內(nèi)核SRAM接口應(yīng)用

- 微控制器環(huán)境要求在盡可能小的封裝里實現(xiàn)最多的通用I/O。存微控制器尺寸和成本的限制下,M4K內(nèi)核內(nèi)部不支持指令高速緩存(I-cache)或數(shù)據(jù)高速緩存(D-cache)的標準功能。但MIPS32 M4K內(nèi)核所具有的一些特點使其非常適用于微控制器應(yīng)用領(lǐng)域。這就涉及到本文重點討論的一個內(nèi)容--SRAM接口,這是MIPS32 M4K內(nèi)核的一個標準功能。 微控制器應(yīng)用需要僅用最少的接口邏輯就可以在處理器內(nèi)核和存儲系統(tǒng)之間實現(xiàn)緊密耦合。MIPS32M4K內(nèi)核SRAM接口就是一個比較完美的解決方案。

- 關(guān)鍵字: 微控制器 I/O MIPS32 SRAM 接口

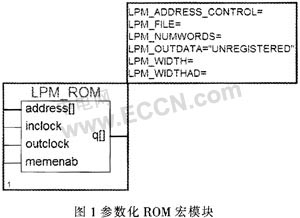

基于FPGA的mif文件創(chuàng)建與使用

- 1 引言 在一些需要特殊運算的應(yīng)用電路中,只讀存儲器ROM是關(guān)鍵元件,設(shè)計人員通常利用ROM創(chuàng)建各種查找表,從而簡化電路設(shè)計,提高電路的處理速度和穩(wěn)定性。FPGA是基于SRAM的可編程器件。掉電后FPGA上的配置信息將全部丟失,所以由FPGA構(gòu)造的數(shù)字系統(tǒng)在每次上電后要依賴于外部存儲器來主動配置或在線被動配置。真正意義上的ROM應(yīng)具有掉電后信息不丟失的特性,因此利用FPGA實現(xiàn)的ROM只能認為器件處于用戶狀態(tài)時具備ROM功能。使用時不必要刻意劃分,而ROM單元的初始化則是設(shè)計人員必須面對的問題。

- 關(guān)鍵字: FPGA ROM mit文件 SRAM

IBM已生產(chǎn)出首個22納米工藝SRAM芯片

- IBM周一宣布,已生產(chǎn)出首個22納米工藝SRAM(靜態(tài)存儲器)單元。 據(jù)國外媒體報道,SRAM芯片是半導(dǎo)體產(chǎn)業(yè)試驗新工藝的設(shè)備,速度更快、體積更小且技術(shù)更復(fù)雜,主要負責在數(shù)據(jù)被處理之前暫時存儲數(shù)據(jù)。 IBM認為SRAM芯片的生產(chǎn)是縮小整個微處理器體積的重要一步。SRAM芯片將使22納米處理器性能大幅提高,并減少耗電。 IBM希望,到2011年能夠制造出22納米制程處理器。IBM研究機構(gòu)副總裁陳博士表示:“隨著處理器內(nèi)核數(shù)量增多,人們對微處理器中存儲器的需求也在日漸增加。為

- 關(guān)鍵字: IBM SRAM 靜態(tài)存儲器 22納米

世界上最小的靜態(tài)存儲單元問世

- 8月18日,美國IBM公司、AMD以及紐約州立大學(xué)Albany分校的納米科學(xué)與工程學(xué)院(CNSE)等機構(gòu)共同宣布,世界上首個22納米節(jié)點有效靜態(tài)隨機存儲器(SRAM)研制成功。這也是全世界首次宣布在300毫米研究設(shè)備環(huán)境下,制造出有效存儲單元。 SRAM芯片是更復(fù)雜的設(shè)備,比如微處理器的“先驅(qū)”。SRAM單元的尺寸更是半導(dǎo)體產(chǎn)業(yè)中的關(guān)鍵技術(shù)指標。最新的SRAM單元利用傳統(tǒng)的六晶體管設(shè)計,僅占0.1平方微米,打破了此前的SRAM尺度縮小障礙。 新的研究工作是在

- 關(guān)鍵字: AMD SRAM IBM 存儲單元

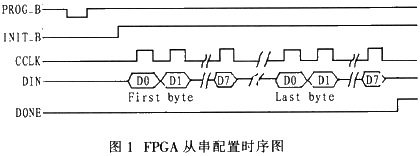

基于ARM的嵌入式系統(tǒng)中從串配置FPGA的實現(xiàn)

- 1 引言 ARM(Advanced RISC Machines)既可以認為是一個公司。也可以認為是對一類微處理器的統(tǒng)稱,還可以認為是一項技術(shù)。基于ARM技術(shù)的微處理器應(yīng)用約占據(jù)了32位RISC微處理器75%以上的市場份額,ARM技術(shù)正在逐步滲入到人們生活的各個方面[1]。到目前為止,ARM微處理器及技術(shù)已經(jīng)廣泛應(yīng)用到各個領(lǐng)域,包括工業(yè)控制領(lǐng)域、網(wǎng)絡(luò)應(yīng)用、消費類電子產(chǎn)品、成像和安全產(chǎn)品等。 FPGA(Field Programmable Gate Array)是一種高密度現(xiàn)場可編程邏輯器件,

- 關(guān)鍵字: ARM 嵌入式 FPGA SRAM

FPGA應(yīng)用愈加廣泛 行業(yè)演進呈現(xiàn)三大趨勢

- FPGA(現(xiàn)場可編程邏輯器件)產(chǎn)品的應(yīng)用領(lǐng)域已經(jīng)從原來的通信擴展到消費電子、汽車電子、工業(yè)控制、測試測量等廣泛的領(lǐng)域。而應(yīng)用的變化也使FPGA產(chǎn)品近幾年的演進趨勢越來越明顯:一方面,F(xiàn)PGA供應(yīng)商致力于采用當前最先進的工藝來提升產(chǎn)品的性能,降低產(chǎn)品的成本;另一方面,越來越多的通用IP(知識產(chǎn)權(quán))或客戶定制IP被引入FPGA中,以滿足客戶產(chǎn)品快速上市的要求。此外,F(xiàn)PGA企業(yè)都在大力降低產(chǎn)品的功耗,滿足業(yè)界越來越苛刻的低功耗需求。 第一時間采用新工藝提升性能降低成本 半導(dǎo)體產(chǎn)品的集成度和成本

- 關(guān)鍵字: FPGA ASIC SRAM 低功耗

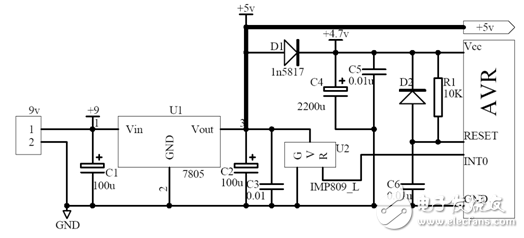

基于DSP的廣播級數(shù)字音頻延時器

- 音頻延時器可用于廣播電臺直播節(jié)目。它將音頻信號延時一段時間后播出,以避免主持人的口誤或聽眾熱線中聽眾的一些不健康言論通過廣播媒體傳播,從而實現(xiàn)直播節(jié)目的安全播出。作為廣播級設(shè)備,音頻延時器對動態(tài)范圍、失真、信噪比和頻率響應(yīng)等性能指標要求很高,因此一般采用數(shù)字技術(shù)。采用計算機內(nèi)置全雙工聲卡硬盤,可以以軟件方式實現(xiàn)音頻信號眨時,但使用操作不方便,可靠性較差,性能價格比較低。本文提出的基于高精度∑-ΔADC和DSP芯片的廣播級數(shù)字音頻延時器,具有性能指標高、操作簡便、功能齊全等特點,該設(shè)

- 關(guān)鍵字: DSP 音頻延時器 ADC SRAM

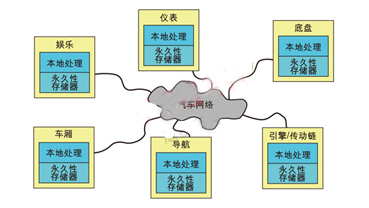

利用永久性存儲器實現(xiàn)智能汽車功能的全面調(diào)用

- 假設(shè)8個月前你駕車駛上了一個帶急轉(zhuǎn)彎的高速公路坡道。由于轉(zhuǎn)彎時速度太快,汽車自動采取了主動安全和懸掛措施來避免駛離道路。 主動安全措施包括汽車制動、電子穩(wěn)定控制和安全帶的預(yù)拉。智能汽車可以記憶曾采取的主動安全措施以及當時的速度、GPS位置和軸承的情況。 現(xiàn)在假設(shè)你的配偶正在前述坡道上駕車行駛,但這次是在下雨天。通過調(diào)用8個月前記憶的坡道位置和車輛軸承情況,以及了解當前路況的濕滑程度,智能汽車能提前采取正確措施來防止汽車滑出坡道并撞上迎面而來的卡車。 上述事例展示了全面調(diào)用(total

- 關(guān)鍵字: 存儲器 智能汽車 SRAM 導(dǎo)航 電子穩(wěn)定控制

飛思卡爾與意法聯(lián)合開發(fā)車載微控制器

- 美國飛思卡爾半導(dǎo)體(FreescaleSemiconductor)上市了配備Power架構(gòu)CPU內(nèi)核“e200z0”的車用32bit微控制器的三個系列“MPC560xP”、“MPC560xS”及“MPC560xB”(英文發(fā)布資料)。這些產(chǎn)品均為與意法合資的意法半導(dǎo)體(STMicroelectronics)聯(lián)合開發(fā)。采用了90nm工藝技術(shù)制造。 MPC560xP系列適用于汽車的底盤及安全控制。主要用

- 關(guān)鍵字: 飛思卡爾 意法半導(dǎo)體 MPC560xS SRAM CPU

靜態(tài)隨機存儲器(sram)介紹

您好,目前還沒有人創(chuàng)建詞條靜態(tài)隨機存儲器(sram)!

歡迎您創(chuàng)建該詞條,闡述對靜態(tài)隨機存儲器(sram)的理解,并與今后在此搜索靜態(tài)隨機存儲器(sram)的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對靜態(tài)隨機存儲器(sram)的理解,并與今后在此搜索靜態(tài)隨機存儲器(sram)的朋友們分享。 創(chuàng)建詞條

熱門主題

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司