- Altera公司(NASDAQ: ALTR)今天宣布,開始提供業界密度最高的收發器FPGA芯片。作為Altera® Stratix® IV GX FPGA系列中發售的第二個型號器件,EP4SGX530比市場上最大的收發器FPGA大60%。該器件提供530K邏輯單元(LE),48個工作速率高達8.5 Gbps的收發器,20.3 Mbits RAM以及1,040個嵌入式乘法器。Stratix IV GX器件面向通信、廣播、測試、醫療和軍事市場等多種應用領域。

Agilent邏輯和協議

- 關鍵字:

Altera,FPGA,收發器

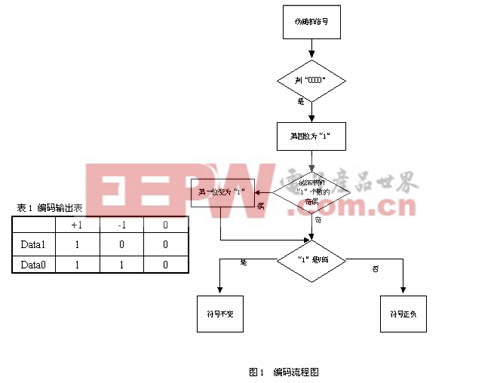

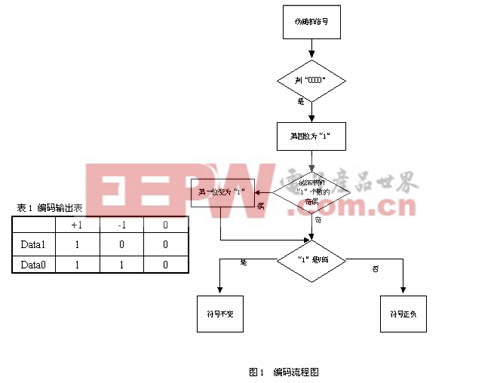

- 基于FPGA的HDB3編解碼器設計,本方案設計模塊可以作為IP(Intellectual Property)核,與嵌入式處理器及其他功能模塊或IP芯核相結合在一片FPGA上構成片上可編程系統SOPC,使得所設計的系統在其規模、可靠性、體積、功耗、性能等方面實現最優化。

- 關鍵字:

設計 解碼器 HDB3 FPGA 基于 編解碼器

- 1 前言 高速以太網可以滿足新的容量需求,解決了低帶寬接入、高帶寬傳輸的瓶頸問題,擴大了應用范圍,并與以前的所有以太網兼容。全雙工的以太網協議并無傳輸距離的限制,只是在實際應用中,物理層技術限制了最

- 關鍵字:

FPGA 高速數據 中繼器

- 近日,賽靈思公司在北京舉辦隆重的25周年慶典,并宣布推出全新一代旗艦產品系列——高性能Virtex? -6和低成本Spartan? -6 FPGA,同時提出了“目標設計平臺”的新理念。

出席慶典和新聞發布會的有賽靈思公司產品營銷高級總監Chuck Tralka,亞太區執行總裁/質量管理和

- 關鍵字:

賽靈思 Virtex FPGA

- 摘要:本文采用FPGA器件EP1C6T144C8芯片代替單片機控制A/D轉換芯片ADC0809進行采樣控制,整個設計用VHDL語言描述,在QuartusⅡ平臺下進行軟件編程實現正確的A/D轉換的工作時序控制過程,并將采樣數據從二進制轉化成B

- 關鍵字:

FPGA 轉換 采樣 控制模塊

- 引言 微控制器在汽車和消費類市場上得到了廣泛應用,能夠以相對較低的成本實現系統高度集成。然而,這類產品也有潛在的成本問題。例如,如果元件功能不符合要求,就必須采用外部邏輯、軟件或者其他集成器件

- 關鍵字:

FPGA 汽車 電子設計

- 介紹基于89S51單片機和FPGA的頻率特性測試儀的設計。該系統設計利用DDS原理由FPGA經D/A轉換產生掃頻信號,再經待測網絡實現峰值檢測和相位檢測,從而完成了待測網絡幅頻和相頻特性曲線的測量和顯示。經過調試,示波器顯示待測網絡頻率范圍100 Hz~100 kHz的幅頻和相頻特性曲線,該系統工作穩定,操作方便。

- 關鍵字:

tt 測試儀 頻率 FPGA 單片機 基于 轉換器

- 安富利公司 (NYSE: AVT) 旗下安富利電子元件部、The MathWorks、德州儀器(TI) 和賽靈思(Xilinx)宣布將舉辦為期2天的協處理SpeedWay設計研討會(Co-Processing SpeedWay Design Workshop™)。研討會將以最新推出的Spartan-3A DSP FPGA / DaVinci開發平臺為基礎,講解如何“用基于模型化的設計方法,進行FP

- 關鍵字:

安富利 德州儀器 FPGA DSP

- 摘要: 本文闡述了通用異步發生器UART 的功能特點,介紹了用硬件描述語言Verilog 來開發各個模塊,并給出仿真結果。本設計使用Altera 的FPGA 芯片,將UART 的核心功能嵌入到FPGA 內部,能夠實現異步通信的功能,可以

- 關鍵字:

FPGA UART 電路設計

- 為保證線陣CCD在圖像測量中正常、穩定工作,必須設計出適合其工作的時序驅動電路。在分析TCDl501D線陣CCD驅動時序關系的基礎上,通過分析CCD輸出的圖像信號,給出了內、外相關雙采樣的時序控制。最后,利用quanus7.2軟件平臺結合VHDL語言進行開發,對所需驅動脈沖進行仿真設計。仿真結果表明,該驅動電路簡單、功耗小、成本低、抗干擾能力強,適用于設備小型化的要求。

- 關鍵字:

FPGA CCD 線陣 驅動

- 簡單介紹了全數字鎖相環(ADPLL)的結構和工作原理,提出一種在FPGA的基礎上可增大全數字鎖相環同步范圍的設計方法,并給出了部分verilog HDL設計程序的代碼和仿真波形。

- 關鍵字:

FPGA 全數字 鎖相環

- RS碼是線性分組碼中一種典型的糾錯碼,既能糾正隨機錯誤,也能糾正突發錯誤,在現代通信領域越來越受到重視。文中介紹基于FPGA使用Verilog―HDL語言的RS(15,9)編碼器的設計方法,并在QuartusII 5.O軟件環境下進行了功能仿真,仿真結果與理論分析相一致,該設計方法對實現任意長度的RS編碼有重要參考價值。

- 關鍵字:

FPGA RS編碼器

現場可編程門陣列(fpga)介紹

您好,目前還沒有人創建詞條現場可編程門陣列(fpga)!

歡迎您創建該詞條,闡述對現場可編程門陣列(fpga)的理解,并與今后在此搜索現場可編程門陣列(fpga)的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473