基于單片機和FPGA的頻率特,tt測試儀

在學(xué)習(xí)《電子線路》、《信號處理》等電子類課程時,高校學(xué)生只是從理論上理解真正的信號特征。不能真正了解或觀察測試某些信號。而幅頻特性和相頻特性是信號最基本的特征.這里提出了基于單片機和FPGA的頻率特性測試儀的設(shè)計方案,可使學(xué)生在實踐中真正觀察和測試信號的頻率特性。

2 設(shè)計方案

該系統(tǒng)設(shè)計采用掃頻測試法。設(shè)頻率響應(yīng)為H(jω),實系數(shù)線性時,不變系統(tǒng)在正弦信號x(n)=Acos(ω0n+ψ)的激勵下的穩(wěn)態(tài)輸出為y(n)。利用三角恒等式,將輸入x(n)表示為兩個復(fù)數(shù)指數(shù)函數(shù)之和:

若輸入為exp(jω0n),線性時不變系統(tǒng)穩(wěn)態(tài)輸出為H(exp(jω0n))exp(jω0n)。根據(jù)線性性質(zhì)可知,輸入g(n)的響應(yīng)v(n)為:

同理,輸入g*(n)的輸出為v*(n)是v(n)的復(fù)數(shù)共軛。于是輸出y(n)的表達(dá)式:

![]()

由上可知,當(dāng)系統(tǒng)在正弦信號的激勵下,輸出響應(yīng)達(dá)到穩(wěn)態(tài),這是與輸入激勵信號頻率相同的正弦波,響應(yīng)信號與激勵信號幅值比為該頻率的幅頻響應(yīng)值,而兩者的相位差為相頻特性值。因此采用掃頻法測量頻率特性。

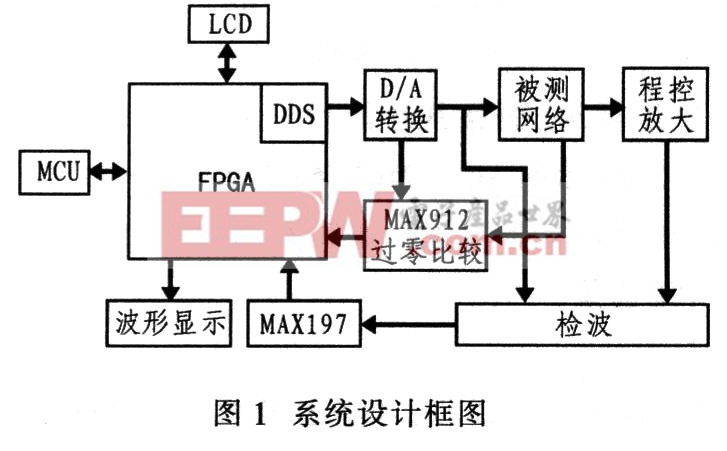

以單片機和FPGA為核心,利用FPGA通過DDS合成得到且頻率由單片機控制的正弦波作為掃頻信號,將其輸入至待測網(wǎng)絡(luò),由峰值檢波電路分別測量各掃頻信號對應(yīng)的輸入網(wǎng)絡(luò)信號和輸出網(wǎng)絡(luò)信號,并由其比例關(guān)系求得待測網(wǎng)絡(luò)的幅頻特性。測量幅度的同時FPGA利用計數(shù)法測量出代表進(jìn)出網(wǎng)絡(luò)信號的相位差的脈沖數(shù),然后送入單片機得到對應(yīng)頻率點的相角。將各頻點得到的幅度特性和相位特性存入FPGA內(nèi)部的RAM中,并結(jié)合鋸齒波顯示在示波器上。同時,LCD還顯示掃描頻率的初始值、終止值和步進(jìn)值。定點測量時,LCD顯示單個頻率點的幅度和相位。該系統(tǒng)設(shè)計框圖如圖1所示。

3 硬件電路設(shè)計

3.1 信號產(chǎn)生模塊

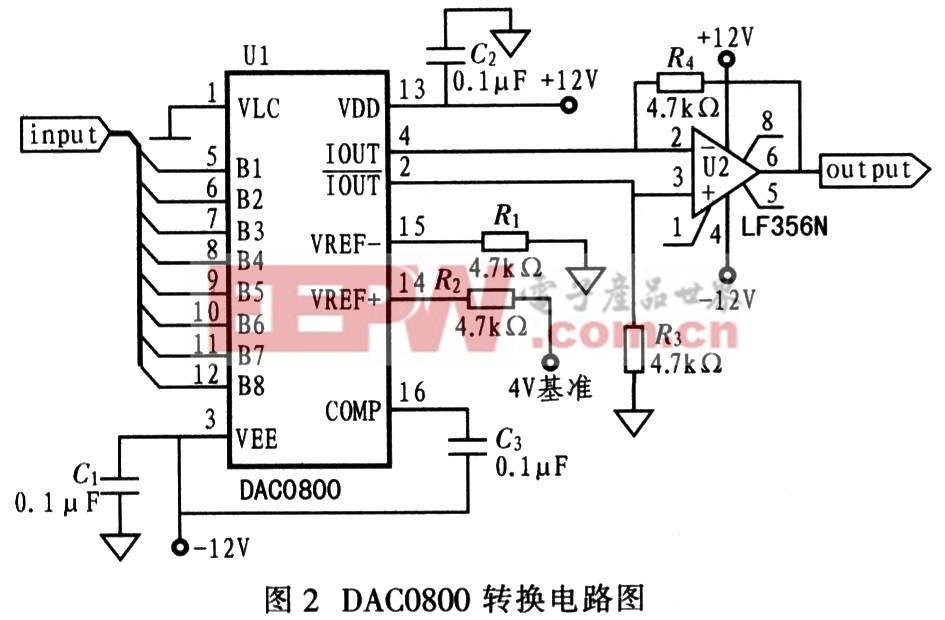

利用FPGA內(nèi)部的DDS信號輸出掃頻信號經(jīng)D/A轉(zhuǎn)換器形成正弦信號。D/A轉(zhuǎn)換器選用DAC0800。DAC0800具有8位分辨率,輸出電流建立時間為100 ns,8位的位寬,工作電壓范圍為±4.5~±18 V。因此,經(jīng)DAC0800所形成的正弦信號有256個取樣值,完全能滿足系統(tǒng)精度要求。輸出正弦信號的最高頻率為200 kHz,100 ns的速率也滿足系統(tǒng)要求。由于DAC0800只具有從數(shù)字量到模擬電流輸出量轉(zhuǎn)換功能,因此.需增加運算放大器實現(xiàn)I―V轉(zhuǎn)換,其轉(zhuǎn)換電路如圖2所示。DDS信號輸出需要加低通濾波器來平滑濾波,以減少信號的諧波分量。

3.2 峰值檢波電路

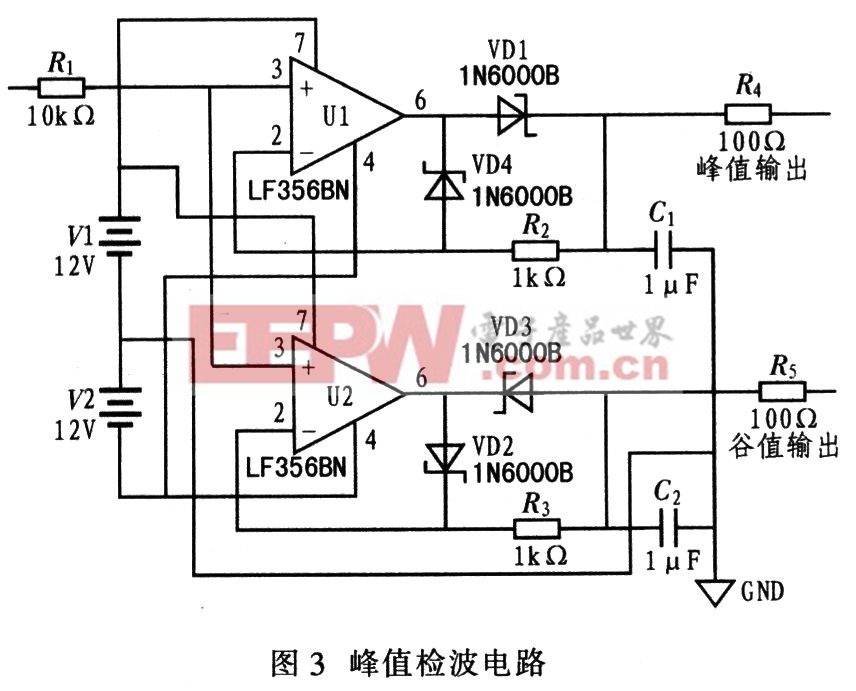

峰值檢測原理是當(dāng)輸入電壓通過正半周時,檢波管導(dǎo)通,電容C充電,選取適當(dāng)電容值,使其電容放電速度大于充電速度,這樣,電容兩端的電壓可以保持在最大電壓處,該電壓通過由運算放大器構(gòu)成的射隨器(高阻隔離)輸出電壓峰值。這里運算放大器選用LF356,其輸入失調(diào)電壓和輸入失調(diào)電流較小,輸入阻抗大,可以很好隔離前后級。峰值檢波電路如圖3所示。

評論