基于賽靈思FPGA的數字頻域干擾抵消器

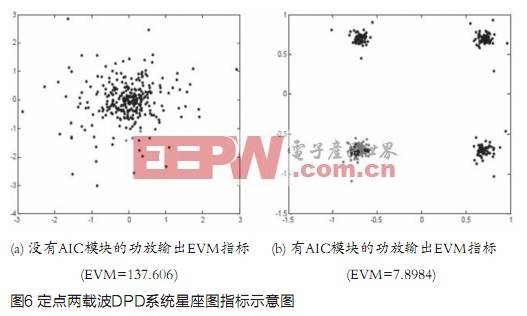

其次,通過量化指標EVM進行比較[3],圖6給出了信干比為-10dB時的EVM指標,可以看出,AIC算法可有效抵消干擾,改善星座圖。

本文引用地址:http://www.104case.com/article/99723.htm

硬件測試說明

在硬件實現時,利用的開發平臺為Virtex II Board。其中V2P30芯片FPGA具有136個硬核乘法器和塊RAM,可滿足自適應濾波算法以及大點數的FFT變換需要大量的乘法器和存儲器的需求。此外,大量的Slice可實現小區搜索模塊以及相關測試平臺的建立。

此外,對于簡易的視頻測試平臺,利用VGA接口完成測試平臺,進行最終的測試驗證。XUP Virtex II PRO板卡帶有高精度的DAC芯片FMS3818,能達到預期目的。軟件開發選用了ISE8.2.03i,相應的Chipscope為8.2版本。

硬件系統需要實現頻域AIC、小區同步搜索、WCDMA信源發生器、測試平臺4大模塊。其中AIC模塊可劃分為大點數的FFT變換以及相應的串并、并串轉換等主要功能。將設計分為5個大的模塊:頂層模塊、AIC處理模塊、信源發生器、小區搜索以及測試平臺。FFT模塊利用賽靈思公司的IP Core(知識產權核)來完成;串并、并串可以利用塊RAM實現;數據處理模塊盡可能地使用SRL16結構來實現,以節省資源。

系統測試按照由部分到整體的思路來完成,首先對各個模塊進行單獨測試,再將部分模塊組合起來完成測試,最后再對整體系統進行測試。這樣,可以將錯誤及早發現并將其消滅在起步階段。測試主要依靠ChipScope來完成,利用其采集數據,再把數據導入MATLAB中,和定點仿真、ModelSim輸出結果進行比較,完成數據分析,從而確保芯片的運行結果和仿真結果是相同的。在測試中,全部以方波測試平臺為基準。

參考文獻:

[1]Widow B, et al, Adaptive noise canceling: principles and applications, Proceedings of the IEEE. 1975,63:1692-1716

[2]Shankar S. Transform Domain LMS Algorithm, IEEE Transactions on acoustics, Speech, and Signal processing. 1983, ASSP-31(3)

[3]田耘,徐文波,等.無線通信FPGA設計[M].北京:電子工業出版社,2008

[4]Haykin S. Adaptive Filter Theory[M].北京:電子工業出版社(影印版),2002

[5]3GPP,TS 25.101,V4.0.0,UE Radio Transmission and Reception (FDD), 2001

WCDMA文章專題:WCDMA是什么意思

評論