基于賽靈思FPGA的數字頻域干擾抵消器

系統方案

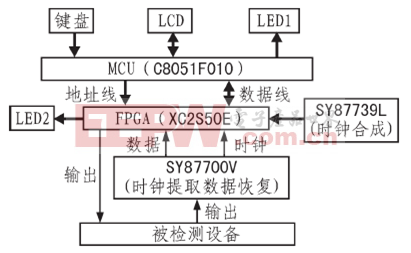

本文引用地址:http://www.104case.com/article/99723.htm完整的系統從數字下變頻后的基帶數據開始,至數字上變頻的前端為止,包括系統同步和干擾抵消兩大組成模塊,系統框圖如圖2所示,其簡要介紹如下:

(1)在沒有干擾的情況下,所采集的數據源從A點輸入,然后將其構造為WCDMA信源,作為頻域干擾抵消模塊的輸入。為了使干擾抵消模塊正確運轉,在本設計中的B點輸出信號為每個碼片4采樣。

(2)為體現頻域干擾抵消的作用,在系統中必須模擬一個干擾信號。本設計將D點的輸出經過功放(PA)作為干擾信號。

(3)將干擾信號經過多徑信道,反饋到B點與WCDMA信號疊加,再進入干擾抵消模塊。為了抵消干擾,將E點的輸出反饋到干擾抵消模塊作為參考信號。在下文中,將此反饋支路稱為輔鏈路;而干擾抵消+功放的鏈路稱為主鏈路。

(4)有干擾的信號經過頻域干擾抵消模塊,輸出抵消后的無干擾信號給同步模塊,即D點。同步模塊進行三步搜索,得到幀頭以及擾碼信息。對同步后的碼片信號進行解擾解擴后得到信息數據,如圖中G點輸出。

(5)在開關1處,可以選擇:有干擾的信號(C點)或者干擾抵消后的信號(D點)輸入同步模塊,并輸出顯示。

(6)在開關2處,可以選擇:數據源直接顯示(A點),或者是同步后解出的數據顯示(G點)。

WCDMA文章專題:WCDMA是什么意思

評論