基于FPGA的遠程圖像采集系統設計

以采集可見光圖像數據為例,上電復位期間 系統處于states0狀態,狀態機用外部輸入的7.375MHz時鐘同步整個運行過程,圖像的幀、行、圖像數據等信號在同步時鐘的下降沿跳變,上升沿鎖存。一幀圖像數據的大小為512×512bit,并將圖像附帶的參數信息寫入圖像數據后一行(即513行),在幀有效期間(states1、states2、 states3狀態),CLK 信號作為行計數器的時鐘,每幀圖像在行有效之前有1行無效圖像信號(states1), 在states2狀態下,控制采集一幀中的前512行,在states3狀態下,采集圖象的參數信息,將圖像數據和狀態參數組合為統一的數據幀,采集完一幀圖像數據后等待下一個幀同步信號的到來。在行有效期(stML_High)控制采集一行中的512個像素點數據,在CLK信號的上升沿進行計數, 在數據有效期間采集完512個像素點,等待下一個行同步信號的到來,按同樣方式對下一行512像素點數據進行采集,直至采集完一幀中的512行。

本文引用地址:http://www.104case.com/article/99680.htm系統仿真

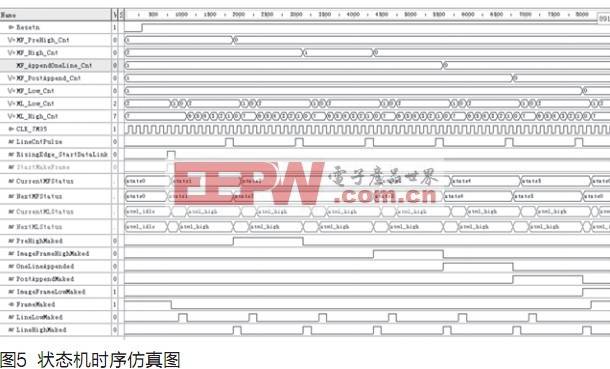

在該系統中,狀態機設計是難點,圖5是運用Active-HDL7.1仿真工具的狀態機仿真結果,仿真時,采用7.375MHz時鐘同步,狀態機啟動后,計數寄存器里的數據遞減,進而產生各狀態轉移滿足的條件,以此實現狀態機的翻轉。

在Active-HDL7.1中編寫TestBench文件時,通過向組幀狀態機計數寄存器寫數,來控制各狀態所占用的時間,利用 StartMakeFrame信號高電平啟動狀態機,各狀態發生翻轉時,狀態完成標志就產生產生高電平跳變。

根據圖5的仿真結果,可以看出組幀狀態機工作正常,所有的邏輯關系也都驗證無誤。

評論