浮點:用 FPGA 嵌入式處理器實現您的構想

賽靈思編譯器支持的 APU-FPU 單精度變量使用的資源較少。當 FPU 被占用時,雙精度操作將通過軟件仿真來執行。

本文引用地址:http://www.104case.com/article/99212.htm軟 FPU 比軟件仿真法平均快 6 倍。單精度 FPU 通常比雙精度快 13%

將 APU-FPU 連接至 PowerPC 440

有兩種方法可將 APU-FPU 連接至 PowerPC 440 處理器:1、利用賽靈思 Platform Studio 設計工具中的 Base System Builder (BSB) 向導;2、將 APU-FPU 單元添加至當前設計方案中即可。

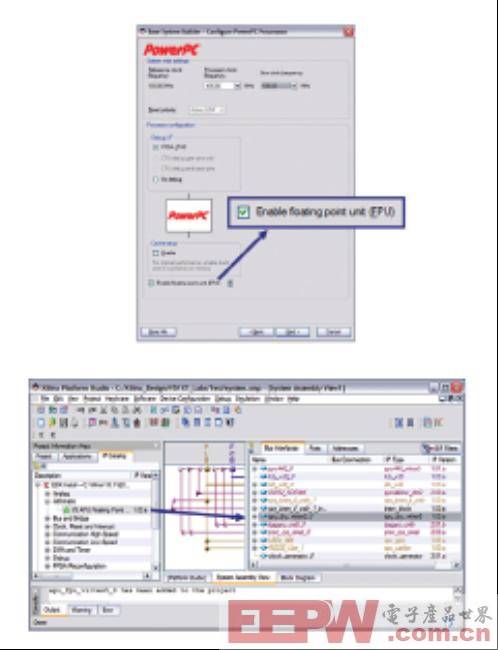

您首先需利用 BSB 向導確定目標板和所期望的處理器(PowerPC 或 MicroBlaze™),然后通過一系列復選框和下拉菜單選擇設計中所需的 IP。借助 BSB 向導,能夠輕松快速地組裝并測試基礎處理器系統。您只需勾選您要選擇的 FPU 框,即可實現APU-FPU 連接(見圖 3 頂部)。該向導可實現一個經過優化能以處理器時鐘三分之一速率運行的雙精度 FPU。您也可定制更高時鐘速率的 FPU 和單精度 FPU。

如果不想使用向導,您也可通過另一種方法來實現,即按照系統組裝視圖拖動 IP Catalog 下的 APU- FPU IP,然后對 FPU 進行配置即可。圖 3 底部圖片顯示了 IP Catalog (見左下方)和系統組裝視圖中新添加的 FPU。右擊 FPU 并選擇 Configure IP,然后您便可選取想要的精度(單精度或雙精度)并確定您希望該 FPU 是針對低時延(三分之一時鐘速率)或是高速率(二分之一時鐘速率)而進行優化;最后將 FPU 連接至 FCB 并將 FPU/FCB 時鐘鏈接至適當的時鐘(通常是二分之一或三分之一處理器時鐘速率。)

圖 3——通過 BSB 向導(頂部)以及系統組裝視圖將 FPU 添加至現有 PowerPC 處理器設計方案中

評論