浮點:用 FPGA 嵌入式處理器實現您的構想

在采用數值處理技術創建嵌入式應用時,通常以整數或定點表示法來確保算術運算盡量簡單,這一點至關重要。因其不僅有助于使成本和功耗降至最低,而且還能盡可能地加速硬件部署。

本文引用地址:http://www.104case.com/article/99212.htmFPGA 非常適用于執行定點運算,并能在邏輯或基于軟件或硬件處理器的實施方案中創建高度并行的數據路徑解決方案。Virtex®-5 FPGA 產品系列中 FXT 系列的最新硬件處理器 Xilinx® PowerPC® 440 可提供超標量功能,讓用戶能夠對器件編程,使其以高達 550 MHz 的時鐘速率并行執行一個或兩個定點運算。

盡管用戶能通過對器件進行編程來執行大多數采用整數或定點算術的運算,但通常須重新運算并插入比例運算以確保計算結果足夠精確。對于復雜運算而言,這不僅耗時,而且還會導致程序變為專用型且不可重用。理想的替代方法是采用標準浮點表示法來提供一種適用于多個應用的高動態范圍。這樣人們就無需修改算法即可獲得適用于任何特定應用或操作環境的定點實施方案,也無需為隨后的項目及應用而大范圍地修改代碼。

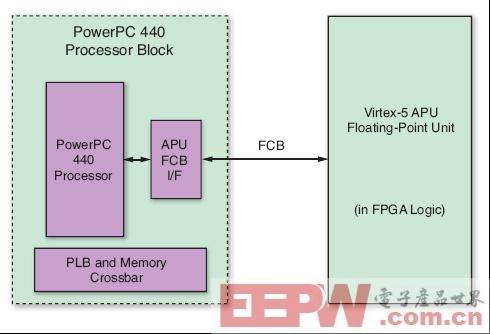

雖然賽靈思為基于 IBM 浮點性能庫的 PowerPC 440 處理器提供了一種行之有效的仿真浮點解決方案,但處理器內核仍需占用數十個周期來執行每條運算。而采用浮點運算單元 (FPU) 形式的浮點運算硬件加速功能可縮短該運算周期。Virtex-5 FXT 系列中的 PowerPC 440 處理器提供了有效接口,能夠將賽靈思軟 FPU 等硬件加速器連接至該處理器內核。該方案可通過結構協處理器總線 (FCB) 將 PowerPC 440 處理器上的 128 位輔助處理器單元 (APU) 接口橋接至協處理器。使用該類協處理器(賽靈思 LogiCORE™ IP Virtex-5 APU-FPU),Virtex-5 FXT 用戶可以選擇軟件仿真或者專用軟邏輯 FPU 在 PowerPC 上自如地實現浮點運算。圖 1 顯示了通過 FCB 將 PowerPC 440 處理器連接至 Virtex-5 APU-FPU 的典型實施方案。

圖 1——包含 APU-FPU 內核的嵌入式處理器系統

評論