Rambus聯合金士頓開發出“線程式內存條技術”

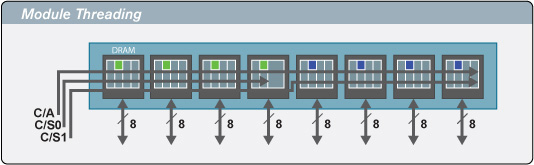

Rambus公司以往的新聞幾乎都與XDR DRAM的官司有關,不過這次他們則和金士頓合作開發出了一種可用于增大DDR3內存帶寬的技術“線程式內存條技術”(Threaded memory module)。這種技術基于現有的DDR3技術,不過將內存條上的內存芯片進行了分塊處理,位于各個分塊內部的芯片共享一個命令/地址端口,不過數據傳 輸部分則可通過各自獨立的傳輸通道進行傳輸,傳輸的位寬可達64字節(512bit),這樣就可以將傳統DDR3內存的帶寬提升50%左右,而且采用這種 技術之后,內存芯片的活躍時間也比過去降低了一半,如此便可節省20%的能耗。

本文引用地址:http://www.104case.com/article/98387.htm

目前單通道DDR3內存的位寬為64bit,雙通道配置則為128bit;而線程式內存條技術則只需單通道便可提供512bit的數據傳輸位寬,這樣理論峰值帶寬便大大提高了,不過按Rambus公司自己提供的實測數據表明,實際的數據傳輸帶寬增加幅度一般在50%以下。

兩家公司將在Intel IDF2009論壇上展示采用這種技術的實際產品。

評論