Spartan-3 FPGA系列中高效PCB布局的LVDS信號倒相

提要

本文引用地址:http://www.104case.com/article/86182.htm在比較簡單的未大量使用過孔的四層或六層 PCB 上,可能很難對 LVDS 或 LVPECL 這類差分信號布線。其原因是,驅動器上的正極引腳必須驅動接收器上的相應正極引腳,而負極引腳則必須驅動接收器的負極引腳。有時跡線以錯誤的方向結束,這實際上是向電路中添加了一個倒相器。本應用指南說明 Spartan?- 3 FPGA 系列如何僅通過在接收器數據通路中加入一個倒相器即可避免大量使用過孔,并且在不要求 PCB 重新設計的情況下即可解決意外的 PCB 跡線交換問題。這項技術同樣適用于將 FPGA 用作驅動器的情況,而且交換跡線可使得在其他器件或連接器上的 PCB 布線更容易。

簡介

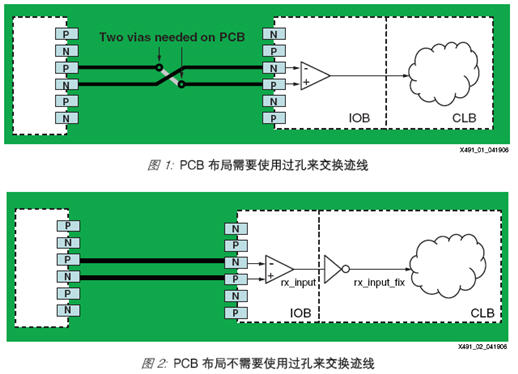

圖1 所示為一個 PCB 示例,其中正極引腳驅動接收器的正極引腳,負極引腳驅動接收器的負極引腳。如果引腳被意外交換,那么 PCB 跡線實際上就變成了一個倒相器,這就可能需要電路板重新設計。

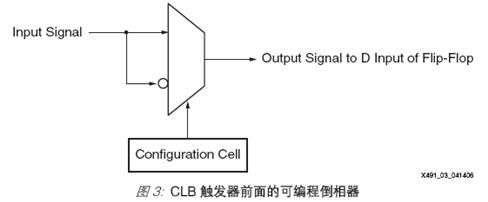

圖2 說明 Spartan-3 FPGA 系列如何通過在接收器數據通路中加入必要的倒相器來解決這一問題。有此功能,設計人員便可以為簡化布線而任意交換跡線。因此,PCB 設計人員可以為實現最大信號完整性而自由布置差分對;所發生的任何交換都可以在 FPGA 內部得到校正。如果使用 DCM (請參閱“異步輸入”),則這一布線的自由僅適用于數據線,而“不”適用于時鐘線。交換線路絕對不會損壞器件。

吸收倒相器示例

在兩種情況下,可以向前吸收倒相器:

1. 當直接驅動觸發器輸入時

2. 當驅動到邏輯函數中時

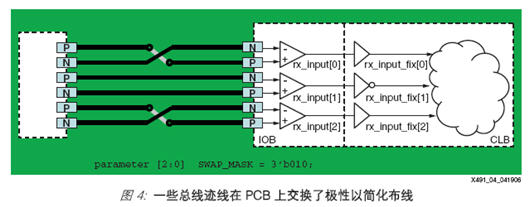

在第一種情況下,Spartan-3 FPGA 系列在 CLB 觸發器的直接 (D) 輸入路徑上有一個多路復用器(如圖3 所示)。此多路復用器在真實輸入信號和補充輸入信號之間進行選擇。它通過一個配置單元進行配置,該單元由加載到此器件中的比特流進行初始化。用戶在操作過程中不能訪問多路復用器。

在第二種情況下,倒相器直接就被吸收了。例如,如果一個執行“B = ~A”的倒相器后面緊跟著一個執行“D = B 與 C”的與門,那么一種簡單的替代方式就是一個無倒相器的執行“D =~A 與 C”的與門;換句話說,就邏輯的利用和延遲而言,倒相器吸收永遠是“自由”的。

這種倒相器吸收的機制也適用于 IOB 輸出觸發器。同樣,如果是為簡化 PCB 布局所需,這種吸收可以“自由”地在 FPGA 的輸出通路中加入倒相器。如果 FPGA 驅動某接插件,而此接插件帶有與此 FPGA 的 N 和 P 兩個 LVDS 輸出直接匹配的預定義引腳,則此機制可以起到幫助作用。

異步輸入

圖2 是可以考慮的最簡單的示例。接收到的經過交換的 LVDS 信號將用在 FPGA 內部的組合邏輯中。在此例中,只需將一個簡單的倒相器添加到代碼中。此倒相器的代碼以 Verilog 和 VHDL語言表述如下:

Verilog: assign rx_input_fix = ~rx_input;

VHDL: rx_input_fix <= not rx_input;

可以將此倒相器吸收到由輸入信號驅動的組合邏輯中,也可以將其吸收到 FPGA 內部的某個觸發器的 D 輸入中,但不能將其吸收到 FPGA 的 IOB 內的觸發器、DCM 或 BUFGMUX 時鐘緩沖器中。因此,引腳交換的靈活性無法用到將用于數據時鐘的時鐘信號上。如果上述時鐘只是系統的振蕩器,那么可以交換線路并且不需要再倒相,這樣做不會產生任何負面效應。

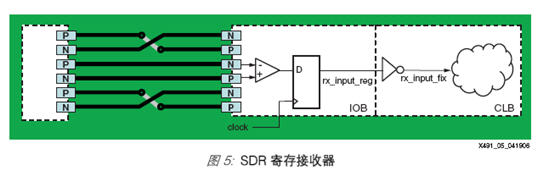

圖4 所示示例中的輸入實際上是一條由“n”個信號對組成的總線。其中某些信號對是正確的,而其他信號對則為了方便而進行了交換。此例中,在設計中最好定義一個對應這“n”個輸入的掩碼。該掩碼用來有選擇地反轉(事實上不包括“與”)那些需要校正的位,但不反轉接收無誤的位。在圖4 中,位 0 和 2 是正確的,而位 1 需要倒相。在代碼中處理校正的最好方式是使用生成環,它們可以例化輸入緩沖器并且有選擇地逐位執行倒相。

以下 Verilog 代碼用生成環來執行接收倒相:

.

parameter [2:0] SWAP_MASK = 3'b010;

.

.

genvar i;

generate

for (i = 0; i <= 2; i = i + 1)

begin: loop0

IBUFDS

#(.IOSTANDARD("LVDS_25"), .IBUF_DELAY_VALUE("0"), .DIFF_TERM("FALSE"))

ibuf_d (.I(datain_p[i]), .IB(datain_n[i]), .O(rx_input[i]));

assign rx_input_fix[i] = rx_input[i] ^ SWAP_MASK[i];

end

endgenerate

以下 VHDL 代碼用生成環來執行接收倒相:

.

constant SWAP_MASK : std_logic_vector(2 downto 0):= "010";

.

.

loop0: for i in 0 to 2 generate

ibuf_d: ibufds generic map

(IOSTANDARD => "LVDS_25", IBUF_DELAY_VALUE => "0", DIFF_TERM => FALSE)

port map

(i => datain_p(i), iB => datain_n(i), o => ; rx_input(i));

rx_input_fix(i) <= rx_input(i) xor SWAP_MASK(i);

end generate;

通過修改紅色的粗體字符,可以方便地將此機制擴展到不同的位寬。

IOB 輸入觸發器的同步使用

通常,輸入信號寄存在 IOB 觸發器中,因為高速數據傳輸是使用 LVDS 的最常見的原因。可使用下列技術之一來寄存數據:

單數據速率 (SDR) 技術,這種技術在 IOB 中只使用一個(通常是正沿觸發的)觸發器或者

雙數據速率 (DDR) 技術,這種技術使用正沿和負沿都觸發的觸發器對輸入數據線進行采樣

在兩種情況下都不可能在輸入放大器和觸發器之間反轉輸入信號,因為 IOB 模塊中的觸發器沒有可倒相的輸入。倒相器需要添加到 IOB 輸入觸發器后,它們可以被吸收到其后的寄存邏輯或組合邏輯中。

SDR 示例

圖5 所示為 IOB 中帶有一個觸發器的 SDR 方案。

以下代碼說明針對相同生成環示例的 SDR 寄存情況。唯一的變化是增加了觸發器例示。

Verilog 語言代碼:

.

parameter [2:0] SWAP_MASK = 3'b010;

.

.

genvar i;

generate

for (i = 0; i <= 2; i = i + 1)

begin: loop0

IBUFDS#(.IOSTANDARD("LVDS_25"), .IFD_DELAY_VALUE("0"), .DIFF_TERM("FALSE"))

ibuf_d (.I(datain_p[i]), .IB(datain_n[i]), .O(rx_input[i]));

FD fd_d (.C(clkin), .D(rx_input[i]), .Q(rx_input_reg[i]));

assign rx_input_fix[i] = rx_input_reg[i] ^ SWAP_MASK[i];

end

endgenerate

VHDL 語言代碼:

.

constant SWAP_MASK : std_logic_vector(2 downto 0):= "010";

.

.

loop0: for i in 0 to 2 generate

ibuf_d: ibufds

generic map (IOSTANDARD => "LVDS_25", IFD_DELAY_VALUE => "0", DIFF_TERM => FALSE)

port map (i => datain_p(i), iB => datain_n(i), o => rx_input(i));

fd_d: fd port map (c => clkin, d => rx_input(i), q => rx_input_reg(i));

rx_input_fix(i) <= rx_input_reg(i) xor SWAP_MASK(i);

end generate;

通過修改紅色的粗體字符,可以方便地將此機制擴展到不同的位寬。

評論