基于FPGA的通信系統(tǒng)基帶驗(yàn)證平臺(tái)的設(shè)計(jì)

1 引言

本文引用地址:http://www.104case.com/article/85609.htm在通信領(lǐng)域尤其是無(wú)線通信方面,隨著技術(shù)不斷更新和新標(biāo)準(zhǔn)的發(fā)布,設(shè)計(jì)者需要一個(gè)高速通用硬件平臺(tái)來(lái)實(shí)現(xiàn)并驗(yàn)證自己的通信系統(tǒng)和相關(guān)算法。FPGA(現(xiàn)場(chǎng)可編程門陣列)作為一種大規(guī)模可編程邏輯器件,體系結(jié)構(gòu)和邏輯單元靈活、集成度高、適用范圍寬,并且設(shè)計(jì)開發(fā)周期短、設(shè)計(jì)制造成本低、開發(fā)工具先進(jìn)并可實(shí)時(shí)在線檢驗(yàn),廣泛應(yīng)用于產(chǎn)品的原型設(shè)計(jì)和產(chǎn)品生產(chǎn)。

與傳統(tǒng)的DSP(數(shù)字信號(hào)處理器)或GPP(通用處理器)相比,FPGA在某些信號(hào)處理任務(wù)中表現(xiàn)出非常強(qiáng)的性能,具有高吞吐率、架構(gòu)和算法靈活、并行計(jì)算、分配存儲(chǔ)以及動(dòng)態(tài)配置等優(yōu)勢(shì),因此非常適合用于設(shè)計(jì)驗(yàn)證高速通信系統(tǒng)的基帶處理部分。

本文提出一種基于Xilinx公司Virtex-Ⅱ系列300萬(wàn)門級(jí)FPGA器件的通信系統(tǒng)基帶設(shè)計(jì)驗(yàn)證平臺(tái),適用于高速通信系統(tǒng)基帶的原型設(shè)計(jì)和相關(guān)算法的實(shí)現(xiàn),并已成功應(yīng)用于基于IEEE 802.1la的OFDM基帶系統(tǒng)設(shè)計(jì)。

2 系統(tǒng)平臺(tái)組成和功能

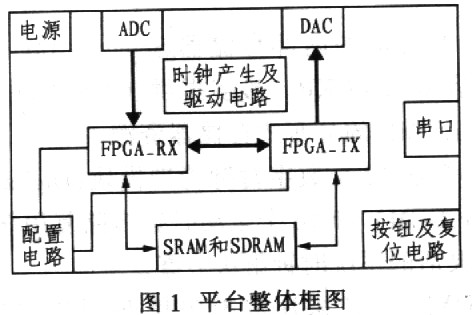

通信系統(tǒng)基帶設(shè)計(jì)驗(yàn)證平臺(tái)主要有以下組成部分:電源部分、FPGA和外圍電路、時(shí)鐘和復(fù)位電路以及模數(shù)和數(shù)模轉(zhuǎn)換電路。平臺(tái)整體框圖見圖1。

各單元模塊的功能如下:

電源部分:負(fù)責(zé)給FPGA和其他電路供電。

FPGA和外圍電路:主要由兩片300萬(wàn)門級(jí)的FPGA器件構(gòu)成,配置電路用于啟動(dòng)后完成對(duì)FPGA的自動(dòng)配置。其他主要外圍電路還有存儲(chǔ)器(SRAM和SDRAM)及串口通信電路。

時(shí)鐘和復(fù)位電路:為FPGA提供系統(tǒng)時(shí)鐘和復(fù)位信號(hào)。

模數(shù)和數(shù)模轉(zhuǎn)換電路:主要是1片用于將數(shù)字信號(hào)轉(zhuǎn)換成模擬信號(hào)的ADC,以及l(fā)片將模擬信號(hào)轉(zhuǎn)換成數(shù)字信號(hào)的DAC。

整個(gè)系統(tǒng)平臺(tái)的工作原理是:兩片F(xiàn)PGA分別設(shè)計(jì)成發(fā)射機(jī)(圖l中的FPGA_TX)和接收機(jī)(圖l中的FPGA_RX)。測(cè)試向量進(jìn)入發(fā)射機(jī)后,經(jīng)過(guò)基帶編碼和調(diào)制,通過(guò)DAC轉(zhuǎn)換成基帶模擬信號(hào)。ADC及接收電路接收電纜傳輸過(guò)來(lái)的信號(hào),將其轉(zhuǎn)換成數(shù)字信號(hào),經(jīng)接收機(jī)解調(diào)和解碼后還原為原始數(shù)據(jù),并與測(cè)試向量比較,獲得誤碼率等性能指標(biāo)。

3 功能單元的電路實(shí)現(xiàn)

3.1 FPGA及其配置電路

VirtexⅡ系列FPGA是Xilinx公司推出的針對(duì)高性能可編程解決方案的首款平臺(tái)級(jí)FPGA器件。Virtex-Ⅱ系列器件采用先進(jìn)的O.15 μm/0.12 μmCMOS 8層金屬混合工藝設(shè)計(jì),內(nèi)核電壓為1.5 V,根據(jù)輸入輸出參考電壓的不同設(shè)計(jì)可支持多種接口標(biāo)準(zhǔn),內(nèi)部時(shí)鐘頻率可達(dá)420 MHz,被認(rèn)為是高速低耗的理想設(shè)計(jì)。

Virtex-Ⅱ系列器件特性:

(1)內(nèi)部時(shí)鐘頻率可達(dá)420 MHz,輸入輸出速率可高達(dá)840MHz。

(2)內(nèi)嵌18x18專用硬件乘法電路和超前進(jìn)位邏輯鏈(Look Ahead Carry)實(shí)現(xiàn)高性能的算術(shù)處理功能。

(3)高性能的內(nèi)部存儲(chǔ)器Select RAM,每個(gè)塊存儲(chǔ)器容量為18 KB。最多提供3 MB的塊存儲(chǔ)資源以及1.5 MB的分布式存儲(chǔ)器資源。

(4)多達(dá)12個(gè)數(shù)字時(shí)鐘管理模塊(Digital Clock Manager,DCM)和16個(gè)全局時(shí)鐘多路復(fù)用緩沖器,提供了靈活的系統(tǒng)時(shí)鐘解決方案。

(5)Virtex-Ⅱ采用數(shù)控阻抗匹配技術(shù)(Digital Controlled Impedance,DCI),可減小因阻抗匹配問(wèn)題而造成的系統(tǒng)不穩(wěn)定,并減小PCB因終端匹配電阻導(dǎo)致的復(fù)雜性。

本平臺(tái)采用兩片300萬(wàn)門的Virtex-Ⅱ FPGA器件,型號(hào)為XC2V3000C,從兼容性和擴(kuò)展性考慮,選用FFl152封裝,該封裝與XC2V4000/6000/8000的FPGA引腳兼容,便于系統(tǒng)升級(jí)。

Virtex-ⅡFPGA的配置信息存儲(chǔ)于SRAM中,掉電后配置信息丟失,上電后需要重新配置下載。Virtex-Ⅱ系列器件配置有5種模式,JTAG/Botmdarv Scan、Master Scrial、Slave Serial、Master SelectMAP、Slave SelectMAP。其中Master SelectMAP和MasterSerial需要使用Xilinx專用的PROM。

本設(shè)計(jì)采用JTAG/Boundary Scan配置模式,主要通過(guò)四個(gè)專用配置信號(hào)線完成所有配置任務(wù)。提供兩種配置方式,一是在線下載配置,通過(guò)下載電纜將FPGA的JTAG口與計(jì)算機(jī)并口相連,使用軟件完成在線下載。另一種是采用SystemACE方案,上電后,通過(guò)SystemACE控制器讀取CF存儲(chǔ)器中的配置文件,通過(guò)JTAG配置相連的FPGA器件。

SystemACE CompactFlash(CF)使用基于CFACompactFlash標(biāo)準(zhǔn)的存儲(chǔ)器,由CompactFlash存儲(chǔ)模塊和ACE控制器組成。ACE控制器具有內(nèi)置的控制邏輯,可以通過(guò)任何一個(gè)ACE控制器接口(CompactFlash接口、CFGJTAG接口、TESTJTAG接口和系統(tǒng)微處理器接口)對(duì)目標(biāo)FPGA鏈進(jìn)行配置。其中CompactFlash接口提供對(duì)CompactFlash存儲(chǔ)卡的支持。單片Virtex-ⅡFPGA所需的配置數(shù)據(jù)大小為300 Kbit-29.O Mbit,這意味著使用一個(gè)Svs-temACE CF方案可以配置超過(guò)250片最大容量的Virtex-Ⅱ系列FPGA。設(shè)計(jì)者可以根據(jù)需要靈活地改變ACE Flash的密度。

評(píng)論