片上系統(tǒng)(SOC)設(shè)計流程及其集成開發(fā)環(huán)境

那么,從板級電子系統(tǒng)設(shè)計到芯片級電子系統(tǒng)設(shè)計轉(zhuǎn)變將導(dǎo)致哪些方面的變化?主要表現(xiàn)在如下幾個方面:

本文引用地址:http://www.104case.com/article/85492.htm(1)在設(shè)計描述工具方面,傳統(tǒng)的板級電子系統(tǒng)設(shè)計主要采用電路原理圖和元器件外形封裝圖作為設(shè)計描述語言工具,而現(xiàn)在的芯片級電子系統(tǒng)設(shè)計主要采用文本方式的硬件描述語言(HDL——Hardware Description Language)作為設(shè)計描述語言工具;

(2) 在設(shè)計流程方面,板極電子系統(tǒng)設(shè)計主要經(jīng)歷電子系統(tǒng)原理圖設(shè)計與仿真、印刷電路板(PCB)設(shè)計與仿真分板(包括信號完整性分析、電磁兼容性分析等)等二個階段,而芯片級電子系統(tǒng)設(shè)計通常需要經(jīng)歷系統(tǒng)級設(shè)計與仿真、算法級設(shè)計與仿真、寄存器傳輸級(RTL)設(shè)計與仿真、邏輯綜合與驗證、版圖設(shè)計綜合與驗證等5個階段;

(3)在軟硬件協(xié)同設(shè)計方面,板級電子系統(tǒng)設(shè)計所采用的方法是先進(jìn)行硬件系統(tǒng)設(shè)計后再進(jìn)行軟件系統(tǒng)設(shè)計的方法,難以實現(xiàn)軟硬同步設(shè)計或協(xié)同設(shè)計,而芯片級電子系統(tǒng)設(shè)計可以比較容易實現(xiàn)軟硬件同時設(shè)計或協(xié)同設(shè)計;

(4)在設(shè)計實現(xiàn)方面,板級電子系統(tǒng)設(shè)計主要基于具有特定功能的集成電路器件,而芯片級電子系統(tǒng)設(shè)計主要是基于具有特定功能的電路模塊——知識產(chǎn)權(quán)核(IP核)。因此,板級電子系統(tǒng)設(shè)計與芯片級電子系統(tǒng)設(shè)計無論是在設(shè)計方法上還是在設(shè)計工具方面都發(fā)生了較大的變化。

隨著現(xiàn)代信息技術(shù)的發(fā)展,電子產(chǎn)品生命周期越來越短,特別是電子工業(yè)技術(shù)不斷發(fā)展,基于深亞微米和超深亞微米的超大規(guī)模集成電路技術(shù)的片上系統(tǒng)(SOC) 芯片需求日益擴(kuò)大,傳統(tǒng)的板級電子系統(tǒng)設(shè)計方法已不能適應(yīng)產(chǎn)業(yè)界對電子產(chǎn)品需求。因此,基于知識產(chǎn)權(quán)(IP)核復(fù)用的芯片級電子系統(tǒng)設(shè)計方法將成為嵌入式系統(tǒng)設(shè)計的主流方式。

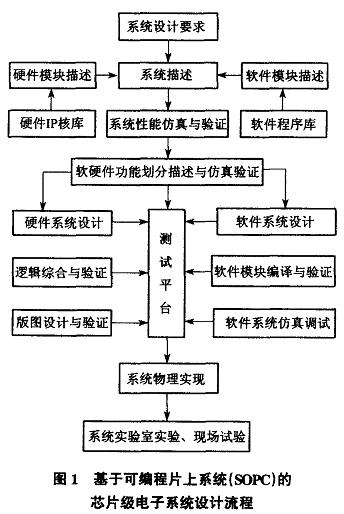

2 基于可編程片上系統(tǒng)(SoPC)的設(shè)計流程

基于可編程片上系統(tǒng)(SOPC)的芯片級電子系統(tǒng)設(shè)計主要有兩大支撐點:可編程片上系統(tǒng)器件所能提供的片上資源和可復(fù)用IP核庫所能提供的IP核資源。其中,可編程片上系統(tǒng)器件所能提供的片上資源是由集成電路工藝技術(shù)發(fā)展決定的,對于系統(tǒng)設(shè)計者來講,應(yīng)根據(jù)設(shè)計要求盡量選擇合適的器件;可復(fù)用TP核庫所能提供的IP核資源需要通過系統(tǒng)設(shè)計者自行建設(shè)。在基于SOC的電子系統(tǒng)設(shè)計中,針對各類專門技術(shù)、專門應(yīng)用、專門工具、專門生產(chǎn)工藝、專門產(chǎn)品的IP資源庫的建設(shè)和共享已形成一種規(guī)范,貫穿在系統(tǒng)設(shè)計的全過程。圖1為典型的基于IP核庫的片上系統(tǒng)(SOC)設(shè)計流程。

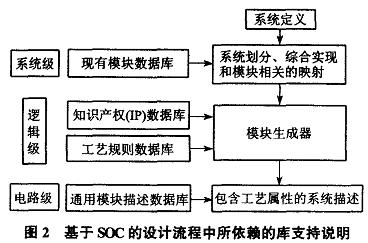

從圖1可以看出,在基于可編程上系統(tǒng)(SOPC)的嵌入式系統(tǒng)設(shè)計流程中,除了需要強有力的EDA設(shè)計工具支持外,離開充分的資源庫的支持,可以說是寸步難行,并且必將失去競爭力。從總體上講,各個層次的IP庫和EDA工具是芯片級電子系統(tǒng)設(shè)計者必備的兩翼,可選的IP核庫資源是一種設(shè)計者能力的表征。圖 2為芯片級電子系統(tǒng)設(shè)計中自頂向下設(shè)計方法的流程中所依賴的庫支持說明。

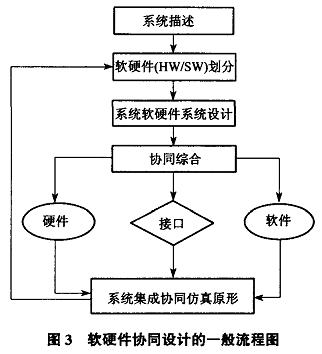

在圖1的片上系統(tǒng)(SOC)設(shè)計流程中,除了需要強有力的IP核庫和EDA工具支持外,與傳統(tǒng)的專用集成電路(ASIC)設(shè)計流程最明顯的區(qū)別就是——軟硬件協(xié)同設(shè)計,圖3給出軟硬件協(xié)同設(shè)計的一般流程。在軟硬件協(xié)同設(shè)計的過程中,傳統(tǒng)的硬件描述語言(VHDL、Verilog HDL)和軟件設(shè)計語言(C/C++)是無法適應(yīng)軟硬件協(xié)同設(shè)計這一種新的設(shè)計方法上的突破,為此必須使用新的系統(tǒng)級描述語言——System C(或其他類似語言)才能完成。

軟硬件協(xié)同設(shè)計通常是從一個給定的系統(tǒng)任務(wù)開始的,通過有效地分析系統(tǒng)任務(wù)和所需要的資源,采用一系列的變換方法并且遵循特定的準(zhǔn)則,自動生成符合系統(tǒng)功能要求的、符合實現(xiàn)代價約束的硬件和軟件框架。這種全新的軟硬件協(xié)同設(shè)計思想需要解決許多問題:系統(tǒng)級建模、系統(tǒng)級描述語言、軟硬件劃分、性能評估、協(xié)調(diào)綜合、協(xié)同仿真和協(xié)同 驗證。

評論