改進混合信號電路的RF性能(06-100)

簡單的子系統

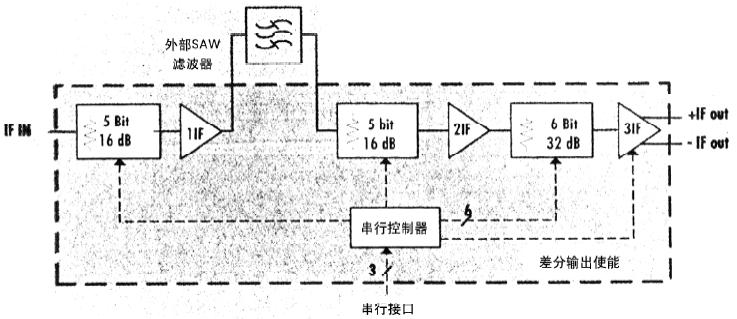

本文引用地址:http://www.104case.com/article/81100.htm 成本、重量和功耗是衛星設計各部分的關鍵因素。典型的商業衛星發射重量成本為$20k/kg,功耗為$20k/w。因此,降低元件數,把功能組合到單個封裝中是非常渴望的。采用UltraCMOS技術為空間應用開發出一個集成子系統,它包括一個IF下變頻器并具有數字增益控制。此器件展示出藍寶石襯底的好處,能實現RF的高集成度,特別是能包含高比例的有源器件。圖1所示的芯片以0.5dB/步給出64dB數字步衰減,集成有3線串引接口,能提供80dB總增益。

最近,根據消費者的要求設計了另一個新的UltraCMOS子系統,它在單芯片上集成3個IF放大器和3個數字步衰減器。所設計的IFOC產品是工作在60~200MHz的數字控制可變增益放大器。其集成設計在單芯片中降低到集成數字步衰減的固定增益放大器,其功耗減小近75%。

減小前置定標器功率

衛星用太陽能板和電池產生、存儲自己本身的電源。因此,設計人員需要特別節省板上電源。因為這會直接影響衛星的壽命。往往冷卻多余熱量與產生熱量同樣花錢多。

用UltraCMOS前置定標器,設計人員在空間應用比采用GaAs器件可節省功耗90%。在UltraCMOS器件使用前,此功能由GaAs器件執行,典型功耗為500mW。

最近,開發的新UltraCMOS前置定標器工作在4~14GHz,是用0.25m UltraCMOS晶體管實現。此器件為衛星制造商提供了靈活的單前置定標器,覆蓋寬頻率范圍。因單芯片前置定標具有相同的工藝技術,所以,所有UltraCMOS前置定標器通路都可無縫的進入UltraCMOS PLL,使系統設計變得容易。

UltraCMOS前置定標器靈敏度在整個頻率范圍內優于+5dBm,在8GHz附近靈敏度大約為-20dBm。衛星制造商可以用高靈敏度區,在所希望的頻率有最佳靈敏度。

在用UltraCMOS實現PLL以前,低成本單片PLL不能滿足像商業衛星這樣的市場需求。除前置定標器和IF子系統外,設計人員工作在UltraCMOS的目的是把這種有前途的技術用到RF混合信號的所有主要功能中。用高集成單片UltraCMOS電路,制造商可降低元件總量數,簡化元件規范和消除對輸入/輸出的關注。所有這些優點將結合到未來更復雜的系統設計中。(京湘)

評論