Altera推出APEX 2系列器件

領先的可編程邏輯器件(PLD)供應商Altera 5月7日宣布推出APEX II系列器件。該系列器件是Altera公司針對可編程芯片上系統(SOPC)應用而開發的新一代高性能、高密度PLD,不僅繼承了大為成功的APEX架構,而且融入了獨特的I/O功能,可直接部署在高性能應用的數據通路中,實現高速通信系統。

本文引用地址:http://www.104case.com/article/2960.htmAPEX II系列器件不僅具有1Gbps True-LVDS特性,而且還結合了額外的624 Mbps Flexible-LVDS通道,可提供多達124條支持高性能差動I/O的輸入和輸出通道。

1Gbps True-LVDS和624Mbps Flexible-LVDS解決方案均支持常用的LVDS、LVPECL、 PCML(準電流模式邏輯)以及等同速率下的HyperTransport接口。

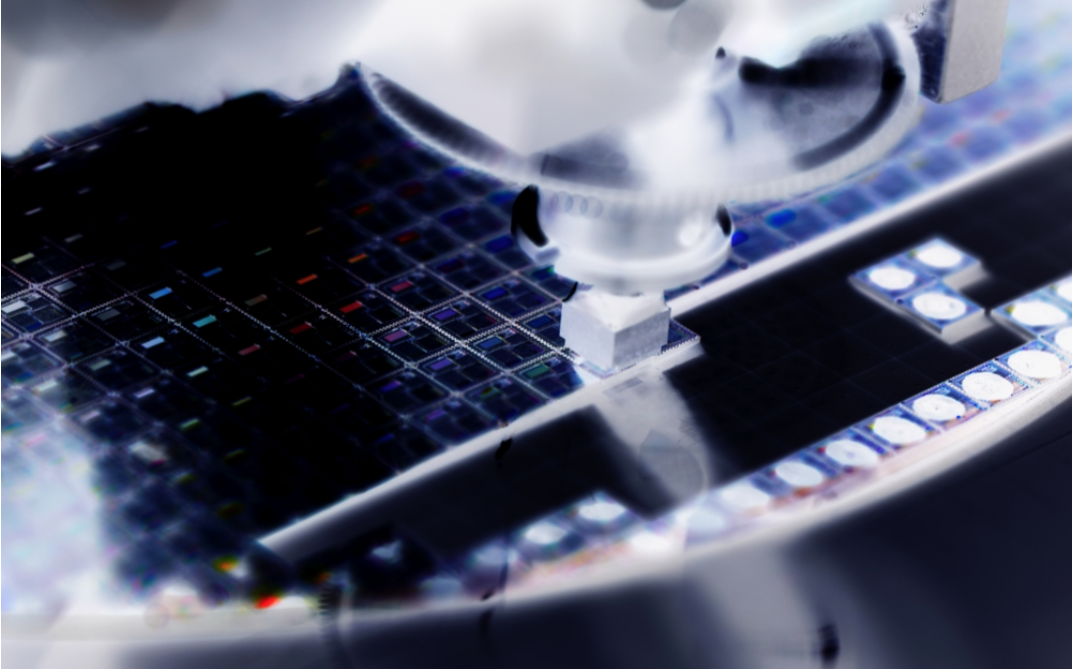

APEX系列器件采用TSMC最新的0.15mm全銅工藝制造。與采用鋁內連工藝制造的器件相比,采用所有層銅互連技術的器件性能可提高30~40%之多。

此外,借助先進的0.15mm晶體管幾何工藝,Altera可在一塊芯片上集成超過8.9萬個邏輯單元和1.5Mbits片上RAM。

APEX II器件的I/O結構在設計時充分考慮到了特殊應用和高速總線接口的需要, 特別是集成了尖端的POS-PHY L4、Utopia L4、Flexbus L4、RapidIO和Hyper Transport支持功能,因此,APEX II器件可與數據通路中的ASSP、包處理器、主處理器或其它器件接口。

APEX II系列器件的密度范圍從16,640邏輯單元和超過400Kbits的片上RAM到89,200邏輯單元和超過1.5Mbits的片上RAM。

完全基于BGA封裝技術,引腳間距有1.27mm和1mm兩種。第一個器件EP2A15將于本季度發布樣品,計劃在2002年中期實現量產。Altera的第四代開發環境,即Quartus? II開發軟件,可向APEX II器件提供開發支援。■ (迎九)

評論